## 論 文

# 기가주파수대 멀티플렉서 설계에 관한 연구

正會員 金 學 善\* 正會員 崔 炳 夏\*\* 正會員 李 亨 宰\*

# Study of the Multigigabit Multiplexer Design

Hak Sun KIM\*, Byung Ha CHOI\*\*, Hyung Jae LEE\* Regular Members

**ABSTRACT** A 4:1 Time Division Multiplexer (MUX) had been designed in using GaAs Source Coupled FET Logic (SCFL), Designed Multiplexer uses a time division frequency divider and two stage of signal combining 2:1 multiplexer. The performance of the multiplexer is verified by PSPICE simulation, Designed circuit operates up to 12.5 Gbit/s with a power dissipation of 192mW, These performance are more advanced than other reported multiplexer in the speed and power dissipation.

#### 1. INTRODUCTION.

Recently digital transmission systems have made rapid progress toward high capacity and high speed. The data transmission rate has entered into the multigigabit range. So a time division multiplexer is a very important block for high speed data manipulation,

For these high speed digital systems, GaAs digital ICs are needed. This circuit was developed for high speed fiber optic application, where output data must have very low jitter at data rate in the gigabit range and input data is most likely to be ECL or ECL compatible format.

Dept. of Avionics Engineering, Graduate School

of Hankuk Aviation University

\*\* 木浦海洋專門大學

Mogpo Merchant Marine Junior College 論文番號: 90-16(接受1989, 10, 20)

<sup>•</sup>韓國航空大學大學院 航空電子工學科

Therefore output data must be retimed with a flip flop and SCFL circuit is suitable to GaAs metal semiconductor FET(MESFET) IC/LSI because of its small Cgd, threshold voltage(Vth) tolerance, high switching and low power dissipation<sup>(1)</sup> (2) (3)

#### 2. CIRCUIT DESIGN

#### 2.1 Basic logic unit

GaAs ICs are composed of normally on or/and normally off MESFETs. Typical normally on ICs are BFL<sup>(4)</sup> and SDFL<sup>(5)</sup> etc.

One of the well known normally off IC is DCFL<sup>(6)</sup>. But this circuit has two major disadvantages ; one is the small Vth margin and the other is a small drive capability against heavy loads of fan outs and interconnection.

To improve a weak point in DCFL LPFL<sup>6</sup> is proposed SCFL<sup>(1)</sup> (2) (3) etc.

To realize high speed, in GaAs ICs with these conventional circuit configurations, the MESFET gate length must be reduced to submicron dimension. However, a fabrication process for GaAs ICs composed of submicron gate MESFET is not complete.

In addition to gate length, one of the factors which have effects on both propagation delay time and transition time is gate to drain cap acitance Cgd. This capacitance is reduced with an increase in drain to source voltage Vds<sup>(6)</sup>. But in conventional circuit it is difficult to reduce Cgd sufficiently.

The reason is that Vds for driver FET only sets logic swing voltage and must be lower than the pinch off voltage when an FET is switched on.

On the other hand, these bias points are adjustable in current mode logics (CML) circ

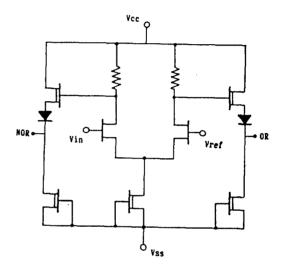

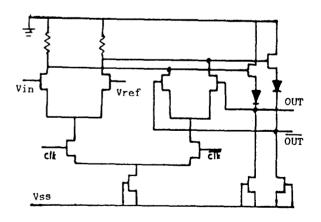

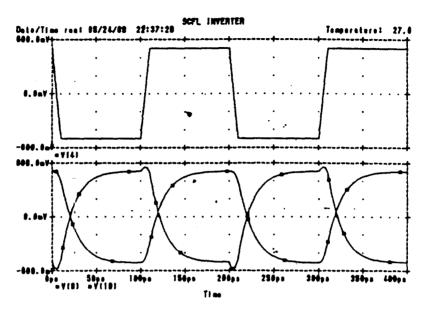

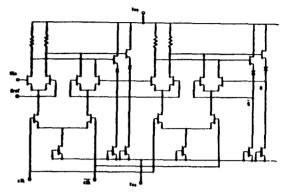

uits. This GaAs CML is called a Source Coupled FET Logic (SCFL). The configuration of the designed SCFL OR/NOR gate and delayed flip flop (D-FF) are shown in Figure 1 and caculated results is shown in Figure 2 Which is simulated by PSPICE (9).

(a) OR / NOR gate.

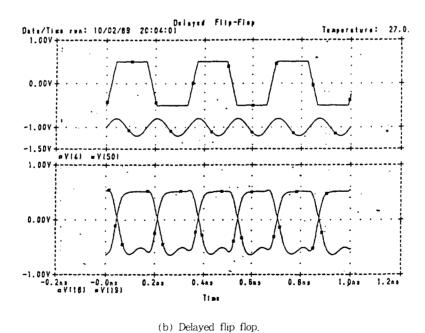

(b) Delayed flip flop.

Fig. 1. Designed schematic diagram of SCFL,

(a) OR / NOR gate.

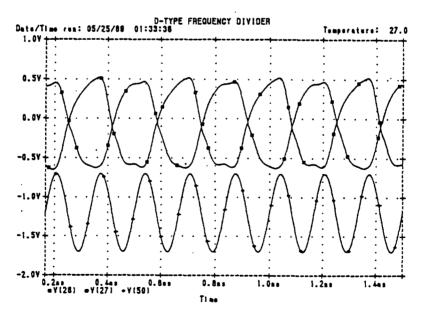

Fig. 2. Calculated output characteristics of designed circuit.

### 2.2 Frequency Divider.

The most important circuit for creating a

multiplexer is the flip flop circuit. The maximum operation frequency of the MUX is

determined by the FF circuit(10),

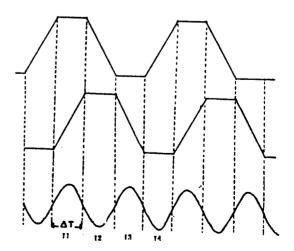

Therefore a frequency divider realized by a Master Slave delayed flip flop(MS D-FF) has a important role in MUX. Maximum output bit rate is defined by the delay time between Master and Slave. Delay time $\Delta t$  is equal to the bit width $\Delta t$  and 1/2 fmax. The configuration of the 2:1 frequency divider is shown in Fig. 3.

In the Master Slave D-FF the data are amplified by Master stage during negative clock periods and the data are generated by Slave stage after two clock cycles. The operations are controlled at a half clock rate<sup>(11)</sup>. The caculated output of the 2:1 frequency divider is shown in Fig. 4

Fig. 3. Clocked MS-D-FF using SCFL.

Fig. 4. Caculated output of the designed 2:1 frequency

### 3. ARCHITECTURE

There are 3 options for achieving high speed

multiplexing that have been considered.

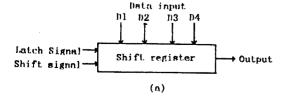

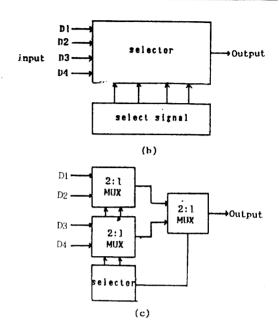

One option is to generate a shift register that loads data parallel for one clock cycle and then shifts it down the register for the three clock cycles<sup>(13)</sup> [see Fig. 5(a)].

This architecture has the advantage that it inherently retimes the data at the output. It is most common approach in GaAs.

The major disadvantages of this architecture are in requirement for high speed clock and the fact that 3 level serise gated logic must be used in the speed limiting path.

The second option[see Fig. 5(b)] is to have a divice which loads all data in parallel and then combines all four channels into single channel using an asynchronous 4 bit MUX gate structure with timing signals generated separately for the select lines<sup>(10)</sup> (15016).

To generate retimed data that output of the channel combining circuit be followed by a flip flop. The down side of this architecture is that speed of operation is likely to be limited by the speed of the output flip flop and delay line and not the 3 level series gated structure.

It should therefore be possible to archieve a higher speed in this architecture than in the first option assuming that ploblem of providing a high speed delay line can be solved.

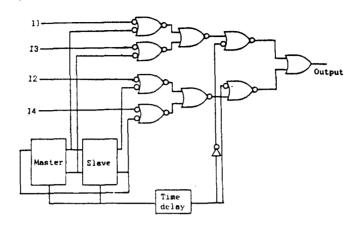

A third option involves loading the 4 bits in parallel and then following this by two stage of signal combining[i, e, two two-one MUXes in series, see Fig.5(c)]. This type of approach can potentially achieve an extremely high data rate because the ECL two to one MUX blocks can be only two level series gate<sup>(17x18)</sup>.

The time slots of the output bit stream are defined only by the sinusoidal select signal and the bit width $\Delta t$  is half the clock period.

Fig. 5. Three alternative architecture.

So we decide upon the architecture that of option #3. Simulation verified that option #3 obtains double data rates compare to other option. Schematic waveform of select signal for cyclical selection of four data chan nels and logic diagram of 4:1 MUX are shown in Fig. 6.

Fig. 6. (a) Schematic waveforms of the three signals for cyclical selection of four data channel.

(b) Logic diagram of the designed MUX

# 4. RESULTS AND FUTURE DIRECTION.

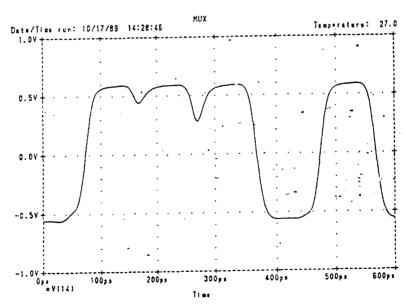

The caculated output of designed 4:1 MUX is shown in figure 7 and performance summary is shown in table(1). Functional die have toggled in response to a standard DC input pattern to a frequency of 6.25GHz and con

firmed to theoretical caculation fmax = 1/2  $\Delta t$ . Therefore maximum output bit rate is 1 2.5 Gbit / s.

This speed is faster than that of reported at date and power dissipation is 192 mW, which is less then that of other 4:1 MUX  $^{\alpha}$

Fig. 7 Output of Designed 4:1 MUX

Table 1 Performance Summary

| Item                    | 4:1 MUX       |

|-------------------------|---------------|

| Gate Length             | 1um           |

| Unit Logic Circuit      | SCFL          |

| Clock frequency(max)    | 6.25 GHz      |

| Input voltage swing     | 1 Vp-p        |

| Output voltage swing    | 1 Vp-p        |

| Total power dissipation | 192 mW        |

| Maximum output bit rate | 12.5 Gbit / s |

However there are a number of specific thing which can be done to increase performance. One thing is to more carefully choose and optimize divices for use in circuit,

Better characterizion and modeling of parasitic package and substrate effects will allow better optimization. Beyond this it will be necessary to develope to more rigorously charactrize interconnect and to develope models more suitable for high frequencies. Technical progress in fabrication(ex. advanced SAINT, submicron, airbridge) is to be applied to simulation parameter.

#### REFERENCES

- M. Idda and et. al., "Analysis of High-Speed GaAs Source Coupled FET Logic Circuits.", IEEE Trans. on Microwave Theory and TECH., Vol. MTT-32, No.1, pp 5~10, JAN. 1984.

- S. Katsu and et. al., "A Source Coupled FET Logic-A New current mode Approach to GaAs Logics.", IEEE Trans. on Electron Devices, Vol. ED-32, No. 6, pp 1114~1118, JUN. 1985.

- THO T. Vu and et, al, "The Performance of Source Coupled FET Logic Circuits that use GaAs MESF-ETs.", IEEE J. of Solid-state Circuits, Vol 23, No. 1, pp 267~287, FEB. 1988.

- R.L. Van Tuyl and et. al., "High Speed integrated Logic GaAs MESFETs.", IEEE J. Solid-state Circuits, Vol. SC-9, pp 269~276, OCT. 1974.

- R.C. Eden and et. al., "Planner GaAs IC Technology : Application for digital LSI.", IEEE J. of Solid-state Circuits, Vol. SC-13, pp 419~426, AUG, 1978.

- H. Ishikawa and et. al., "Normally-off type GaAs MESFET for low power high speed logic circuits.", In Tech. Dig, Int. Solid-state Circuits Conf., pp 200 ~201, FEB. 1979.

- G. Nuzillat and et. al., "Quasi-Normally off MESFET Logic for high performance GaAs IC's.", IEEE Trans. on Electron Devices, Vol. ED-27, pp 1102~1109, JUN. 1980.

- 8. M. Shur, "GaAs Divices and Circuits.", pp 352, 198 7.

- Microsim Corporation., "Pspice", Tustin, JAN. 198

6.

- K,tanaka and et, al., "4:1 Multiplexer and 1:4 Demultiplexer,", OKI Technical Riview, Vol. 23, pp 46~50, OCT, 1987.

- T. Takada and et. al., "An 11-GHz GaAs Frequency Divider Using Source-Coupled FET Logic,", IEEE Electron Device Letters, Vol. EDL-7, No.1, pp 47~4 8, JAN, 1986.

- K. Osafune and et. al., "GaAs Ultra-High Frequency Dividers with Advanced SAINT FET's,", IEEE Trans. On Electron Devices, Vol. ED-33, No. 12. pp 2059~2063, DEC. 1986.

- G. Flower and et. al., "A 3 Gigabit 4:1 Time Division Multiplexer with output retiming." IEEE 198'

Bipolar Circuits and Technology meeting, pp 14 6~149.

- L. Ronn, "Multigigabit Multiplexer Design,", Electron Letters, Vol. 24, Noll, pp 667~669, MAY 1988.

- J. Kemps and et. al., "1.5 Gbit/s GaAs Multiplexer and Demultiplexer forge fast fiber optic links, " Electron Design, Vol. 34, No.2 pp. 107~110. JAN 1986.

- 16. N. Yoshikai and et. al., "Monolithic integrated 4:1

multiplexer and demultiplexer operating up to 4.8 Gbits/s.", Electron Letters, Vol. 21, No. 4, pp. 14 9~151, FEB, 1985.

17. R. Reimann and et. al., "A Time Division Multiplexer IC for Bit rates up to 6 Gbit/s Based on standard Bipolar Technology.", IEEE J. of Solid-State Circuits, Vol. SC-21, No.5, pp. 785-789, OCT. 1986.

18. D. Clawin and et. al., "Silicon Bipolar Decision Circuit Handling Bit rates up to 5 Gbit/s.", IEEE J. of Lightwave Technology, Vol, LT-5, No. 3, pp. 348 ~354, MAR, 1987.

**金 奉 著(Hak Sum KIM)** 正會員 (1959年6月3日生

1986年2月:韓國航空大學 航空電子工

學科 卒業

1990年2月:韓國航空大學院 卒業(工學 碩士)

1987年3月:정석航空工業高等學校教師

主關心分野: 電子回路設計및 GaAs 를 利用한 더지를回路設計 및 시물레이션.

李 亨 宰(Hyung Jae LEE) 正會員

1933年 3 月20日生

1958年3月:韓國航空大學電子工學科卒

~

1961年3月:漢陽大學校工科大學電氣工

學科 卒業

1972年2月:漢陽大學校大學院 修了(工

學碩士)

1988年2月:慶熙大學校 大學院(工學博

t:)

1964年10月:韓國航空大學助教授 1971年7月:韓國航空大學副教授 1978年1月(現在):韓國航空大學教授 1981年4月~1984年12月:本學會副會長

**崔炳 夏(Byung Ha CHOI)** 正會員 1945年6月10日生

1969年:韓國航空大學 航空電子 工學科

卒業(工學士)

1983年:建國大學校 大學院 電子工學科

(工學碩士)

1988年8月:韓國航空大學大學院 航空

電子工學科 博士課程 1987年:電氣通信技術士

1969年:海軍將校

1972年9月~現在:木浦海洋專門大學 教授