## 論 文

# A High-Speed Thinning Processor for Character Recognition System

Yong Seop KIM, Min Suk KIM, Yang Sung JOO, Soo Won KIM Regular Members

문자인식 시스템을 위한 고속 세선화 장치

正會員 金 鎔 燮\* 正會員 金 玟 錫\* 正會員 朱 洋 成\* 正會員 金 壽 遠\*

### **ABSTRACT**

We propose, in this paper, a new thinning algorithm and demonstrate its effectiveness with some concrete experimental results. This new thinning process can solve the problems of disconnectivity and end-point reduction explored in one-pass algorithm. Furthermore, this algorithm is proven effective particularly in high speed operation. A processor for this algorithm, that is capable of handling input image width(between 25 and 40 bits) and also operates on pipelining, is implemented and tested. Flexibility and high speed operation of this thinning processor should find excellent applicability in various areas.

#### 要約

본 논문에서는 새로운 세선화 알고리뉴을 제안하고 실험결과를 통해 알고리뉴의 효율성을 증명하였다. 새로운 세선화 알고리듬에서는 기존의 one-pass 알고리듬에에서 드러난 불연속점과 끝점 감소의 문제점을 해결하였다. 특히 본 알고리듬은 하드웨어 구현에 보다 적합하며 고속 동작이 가능하도록 설계되었다. 구현된 하드웨어 장치는 가변하는 입력 이미지 너비 (25·40 bits)에 선택적으로 대용할 수 있는 실용적인 측면이 있으며 파이프라인 방식으로 고속 동작한다. 본 세선화 장치는 가변 이미지 크기에 대한 융통성과고속동작의 특성을 가지므로 문자 인식 시스템을 포함한 다양한 이미지 처리분야에서 매우 실용적으로 적용할 수 있다.

#### I. Introduction

It is well known that one of the key problems in pattern recognition area is extracting distinctive features from the input patterns. A pattern itself consists of lots of data bits, many of which can be deleted from the image without distorting

\*高麗大學校 電子工學科 Dept. of Electronic Eng., Korea University. 論文番號: 92-16(接受1991, 10, 5) the information. In other words, through the process called "thinning" the number of data of an input pattern can be significantly reduced without losing any stroke features.

Thinning algorithms are commonly classified into (1) sequential and (2) parallel [15] algorithms. Sequential algorithm uses previous pixels to determine current output, parallel algorithm utilizes current neighbor pixels to do the same. In many practical applications the latter is preferred mainly due to its simplicity and hardware feasi-

bility

Most existing parallel thinning algorithms carry out multi passes per iteration; each pass is an independent operation to determine whether or not to remove the boundary and for corner pixels (for a direction). In these operations 3x3 window is generally used, since this particular size has been considered effective. The problem, however, lies in that the connectedness over the edges of input pattern is not guaranteed by using 3x3 window. Hence, to extract better skeleton, additional windows have to be used. These windows show improved results, but they, too, display end-point reduction and disconnected feature in some specific conditions, which are indeed serious problems in character recognition system. Therefore, for the lack of better solution, algorithms with stringent conditions are adopted in character recognition at the cost of processing time

Many thinning algorithms focus on the performance of algorithm itself while neglecting other relevant factors such as hardware feasibility, processing time, and cost, etc., and it is often noticed that these algorithms are not easily implemented in hardware due to cost and/or technical limitations. Furthermore, existing hardware processors are designed to operate only for the fixed image-width, which demands the time-consuming "normalization process," commonly known as a bottleneck phenomenon for its slow speed,

Hence we propose an improved thinning algorithm and processor that is flexible over an image-width. Experimental results prove its outstanding applicability in various pattern recognition systems.

## II. Modifed Thinning Algorithm

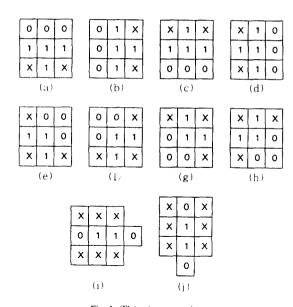

In a thinning process, as shown in Fig.1, eight templates are used over eight directions Eight neighbor pixels around the center will determine the removal of center pixel, Four templates, Fig. 1(a d), are used to delete boundary pixels and Fig.1(e-h) are used to remove corner pixels from each directions. These windows are simultaneously applied unto an input image. When input pattern matches any one of thinning templates, center pixel "1" will be removed. Therefore, two boundary pixels can be removed after an iteration. But in conventinal 3x3 windows, connectedness of the skeleton is not preserved. Therefore, additional 1x4 and 4x1 windows<sup>[6]</sup> are used to save the center pixel "1" when any pattern matches any one of these two additional windows in Fig.1(i) and /or(j).

Fig. 1. Thinning templates.

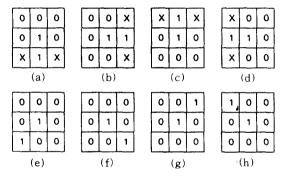

Noise immunity, which is also an important factor of thinning process, is closely related to recognition rate and speed. Thereforeg additional eight templates are used to clean the noise pixels of input image. Due to these trimming templates shown in Fig.2, however, the end points of the objects are no longer preserved. Consequently, an open feature object can be converged into a single dot after a number of iterations because

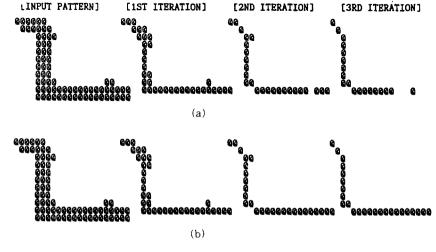

the trimming templates will treat the two end points as noise pixels. In certain situations, connectivity may not be conserved. An example representing these situations is shown in Fig.3. This phenomenon happens due to the templates in Fig.2(a) and Fig.1(c). Also when Fig.1(d) is applied after Fig.2(b), disconnectivity and/or end-point reduction may occur.

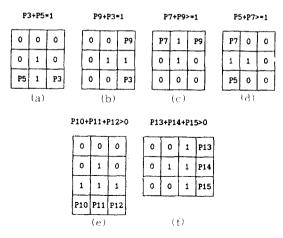

We have developed a few conditions that car resolve these problems. In other words, we have modified trimming templates, Fig.2(a-d) into those of Fig.4(a-f). Fig.4(a-d) are designed to protect end-point reduction and Fig.4(e,f) are to

Fig.2. Trimming templates.

avoid disconnectivity in some situations as shown in Fig.3(a). In those situations like that, extra pixels, P10, P12, P13, P15 are used to help determine the removal of center pixel. And other templates, Fig.2(g-j) are still useful and included in modified trimming templates. As a result, the end-point reduction is disappeared, and disconnectivity problem is resolved with the modified templates as shown in an thinned result, Fig.3 (b).

Although these extra conditions shown in Fig.4 need more hardware, they do not affect the speed of thinning processor because these windows are applied in parallel with the thinning templates. It is apparent that the improved result is easily attainable with these modifications.

# III. Implementing Hardware for Variable Image-Width

Many pattern recognition systems adopt "thinning" as one of the required processing steps since reducing the number of data is crucial requirement for high speed application. In many thinning algorithms, however, it is assumed that image-width of input pattern is constant, But it is

Fig.3. Effects of the thinning templates (a) in <sup>[6]</sup> (b) in modified algorithm,

Fig.4. Modified trimming templates.

not practical to expect the fixed-width image, particularly in a character recognition system, in which the sizes of characters variously differ according to shape, style and font size.

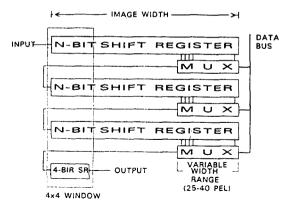

A processor with a capability of handing variable image width<sup>[7]</sup> can be implemented with switchable 16-bit multiplexers. This processor consists of a neighbor pixels generator and a thinning logic. Neighbor pixels generator, which consists of shift-registers and multiplexers as shown in Fig.5, holds neighbor pixels around the center; and thinning logic does instinctive translation from all templates. This thinning processor is implemented by PLD and discrete devices, and it is interfaced to IBM Personal Computers.

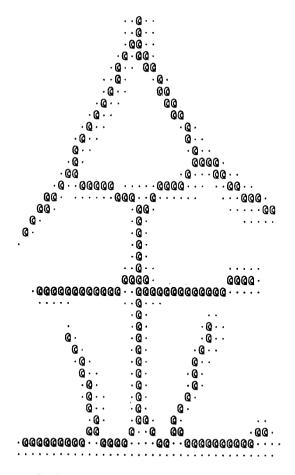

During single WRITE operation, host computer sends information of variable image-width to the processor and makes multiplexer switch from previous image-width setting. A thinning logic and a neighbor pixel generator are implemented by an EPLD and TTL logic gates, respectively. We have built an add on type thinning board and tested it for various input images. A typical 38x38 image is tested with these thinning board, as a result, a thinned image is obtained as shown in Fig.6. Experimental results of the input images with various width and thickness are summarized in Table, 1.

Fig.5. Neighbor pixels generator.

Fig.6. Thinned result of Chinese character '金'

Table 1. Experimental results

| Input Pattern | Image Size     | # of<br>Iteration | Processing<br>Time(ms) |

|---------------|----------------|-------------------|------------------------|

| ʻg'           | 22×28          | 3                 | 1.1                    |

| 'e'           | 34×30          | 7                 | 2,5                    |

| 'T'           | $40 \times 35$ | 5                 | 3.2                    |

| '金'           | 38×38          | 4                 | 2.8                    |

#### IV. Conclusion

In this paper, a modified thinning algorithm has been proposed and its validity demonstrated. Experimental results show that this modified al gorithm preserves the connectivity and the end-points, which are critical requirements in character recognition system. A programmable and fiexible thinning processor has been designed to handle the input pattern regardless of its image-width. We have interfaced the realized prototype processor with IBM PC 286/386 and tested it for the variable image width from 25 to 40-bit. It is proved that processing speed is limited only to the propagation delays of logic gates, since input image continuously enters the processor without control signal. The processing speed is measured to be 2.1ms for four iterations of a 32x30 image at IBM PC 386, 20MHz clock-rate. Experimental results confirms that this modified algorithm and processor is exceptinally effective in various application areas.

#### References

- T. Y. Zhang and C. Y. Suen, <u>A Fast Parallel Algorithm for Thinning Digital Patterns</u>, Communications of the ACM, Vol.27, No.3, pp. 236-239, 1984

- N. J. Naccache and R. Shinghal, SPTA: A <u>Proposed Algorithm for Thinning Binary Pat-</u> <u>terns</u>, IEEE Trans. on Systems, Man and Cy-<u>bernetics</u>, Vol.SMC-14, No.3, pp.409-417, 1984

- 3. C. Arcelli and G. S. Di Baja, <u>A Width-Independent Fast Thinning Algorithm</u>, IEEE Trans. on Pattern Analysis and Machine Intelligence, Vol.PAMI-7, No.4, pp.463-467, 1985

- 4. C. M. Holt and A. Stewart, An Improved Parallel Thinning Algorithm, Communications of the ACM, Vol.30, No.2, pp.156-160, 1987

- P. S. P. Wang and Y. Y. Zhang, <u>A Fast and Flexible Thinning Algorithm</u>, IEEE Trans. on Computers, Vol.38, No.5, pp.741-745, 1989

- R. T. Chin and H. Wan, <u>A One-Pass Thinning Algorithm and Its Parallel Implementation</u>, Computer Graphics Image Processing, Vol.40, pp.30-40, 1987

- 7. Yong-Seop Kim and Soo-Won Kim, Implementation of Size Variable High-Speed Thinning Processor, JTC-CSCC'91, Hiroshima, Japan, pp.60-63, July 1991

**金 鎔 變(Yong Seop KIM)** 正會員 1964年 9 月 9 日生

1988年8月:高麗大學校 大學院 電子電算工學科卒業

(工學土)

1990年8月:高麗大學校 大學院 電子工學科 卒業(工

學碩士)

1990年 9 月~現在:高麗大學校 大學院 電子工學科博士 課程 **金 玟 錫**(Min Suk KIM) 正會員 1967年 9 月20日生

1990年2月:高麗大學校 大學院 電子電算工學科卒業 (工學士)

1992年2月:高麗大學校 大學院 電子工學科 卒業(工 學碩士)

現在: 三星전관(주) 在職 中

**朱洋成(Yang Sung JOO)** 正會員 1967年9月18日生

1990年2月:高麗大學校 大學院 電子電算工學科卒業 (工學士)

1992年2月:高麗大學校 大學院 電子工學科 卒業(工 學碩士)

現在:金星 ELECTRON(予)在職中.

**金壽遠**(Soo Won KIM) 正會員 1952年1月10日生

1974年2月:高麗大學校 大學院 電子工學科 卒業(工 學士)

1981年~1983年:TEXAS A&M University 電子工學 (工學碩士)

1983年~1987年:TEXAS A&M University電子工學 (工學博士)

1987年9月~現在:高麗大學校 電子工學科 副教授