# A New Syndrome Check Error Estimation Algorithm and Its Concatenated Coding for Wireless Communication

Moon Ho Lee\*, Jin Su Chang\* and Seung Bae Choi\* Regular Members

#### **ABSTRACT**

A new SCEE(Syndrome Check Error Estimation) decoding method for convolutional codes and concatenated SCEE/RS (Reed-Solomon) coding scheme are proposed. First, we describe the operation of the decoding steps in the proposed algorithm. Then deterministic values on the decoding operation are drived when some combination of predecoder-reencoder is used. Computer simulation results show that the computational complexity of the proposed SCEE decoder is significantly reduced compared to that of conventional Viterbi decoder without degradation of the  $P_{\ell}$  performance. Also, the concatenated SCEE/RS decoder has almost the same complexity of a RS decoder and its coding gain is higher than that of soft decision Viterbi or RS decoder respectively.

Key words: Syndrome check error estimation, Concatenated SCEE-RS decoding, Low complexity.

# I.서 론

Error correction coding is essentially a signal processing technique that is used to improve the reliability of communication on digital channels[1] [2]. It is because of the received data with errors when digital data are transmitted over a noisy channel.

The convolutional encoding and Viterbi decoding thus have been used in communication fields, especially in wireless communications such as satellite or CDMA systems requiring their powerful coding gain.

The commonly employed Viterbi decoding scheme is optimal in the maximum likelihood sense for decoding convolutionally encoded data but has computational requirements that increase exponentially according to its constraint length. Thus, in high speed applications,

their complexity, large power consumption and expensive cost[1]-[5].

In order to reduce the hardware complexity and power consumption in recent years, many simplying

wider use of Viterbi decoders has been prevented by

In order to reduce the hardware complexity and power consumption, in recent years, many simplying schemes for Viterbi decoder have been proposed. In practice, two approaches, the traceback method and SST(Scarce-State-Transition) type method, are very useful for survivor memory management. Among them, the best one is the SST type Viterbi decoder proposed by Kubota et al. [4][5].

Therefore, we propose a combinational predecodereencoder type decoder, called the SCEE decoder, for the convolutional code with code rate R=1/2 and constraint length K=7. The SCEE decoding scheme is development of the SST-type decoding scheme. Because the proposed decoder has a very simple architecture, it can be used for the concatenation of other codes. Then this concatenated scheme has a higher coding gain and very lower complexity. Thus,

論文番號:97042-0204 接受日字:1997年 2月 24日

<sup>\*</sup>Dept. of Inform. & Commun. Eng., Chonbuk National Univ

we proposed a new concatenated SCEE/RS coding scheme, and analyze its performance for wireless communication systems.

#### II. Viterbi decoders Reviewed

#### A. Conventional SST type Viterbi decoding Algorithm

The implementation of the traceback method Viterbi decoding algorithm has attracted a great deal of interest in many applications, but the excessive hardware/time consumptions caused by the dynamic and traceback decoding procedures make it difficult to design efficient VLSI circuits for practical applications[1][2]. To reduce both hardware size and power consumption, a newly developed SST Viterbi decoding scheme has been Proposed[4][5]. An SST type Viterbi decoder with R = 1/2 and K = 7 for 3bit soft decision data is composed of a conventional Viterbi decoder, and some additional circuits (predecoder, re-encoder, delay circuit, and modulo-2 adder) at the input of the conventional Viterbi decoder. With the SST scheme, the state which corresponds to all "zero" almost always has the largest path metric. Thus, the SST type Viterbi decoding scheme enables the omission of final decision circuit and to reduce the required path memory length without degrading the Pe performance. This leads to a significant hardware reduction in the Viterbi decoders, although the SST scheme requires some additional circuits.

Moreover, in the SST type Viterbi decoder, data stored in the path memory circuits are almost always "zero", except the data affected by channel errors. Thus ON/OFF switchings of gates rarely occur in the path memory circuit. Therefore, power consumption of a CMOS SST type Viterbi decoder is significantly less than that of conventional decoders. For example, at an information rate of 25 Mb/s and a bit-errorrate (BER) of 10<sup>-4</sup>, a power consumption reduction of 40% can be achieved by the system when compared with a conventional Viterbi decoder[4].

# III. SCEE Decoding Algorithm and Its Concatenated Scheme

### A. SCEE Decoding Algorithm

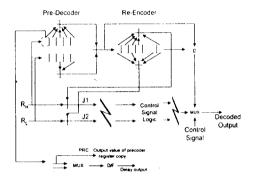

We propose a new decoding method, called SCEE, using maximum convolutional effect as shown in Fig. 1. Here, convolutional effect is an extension of errors, if they are exist before decoding, in decoding due to convolutional encoding. It seems to be spread and despread according to the correlation between the received sequence and the predecoded data in our proposed SCEE decoder.

In relation to convolutional encoding, the Viterbi decoding algorithm is redundant because of the inefficient use of convolutional effect in received sequence. Thus, the major idea in our proposed decoder is to use as a syndrome the extension of errors occurred over the transmission channel and this is a factor contributed for the performance increment of a decoder in Shannon's channel coding theory[1][2]. On the other hand, syndrome decoder employing formers at the input of Viterbi decoder have been proposed to simplify the hard decision Viterbi decoder[6][7]. In comparison with the conventional Viterbi decoder, the syndrome decoder has fewer metric combinations, and can thus be implemented using less hardware [7]. However, the major difference of our proppposed SCEE decoder cor compared to der compared to of our proppposed SCEE decoder compared to er compared to to to the syndrome decoder is that the SCEE decoder estimates error-position by control signals due to the OR-operation of channel errors while the syndrome decoder operates according to the state of the syndrome former[6][7][19]-[21].

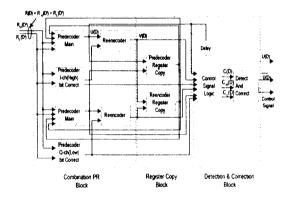

The SCEE decoder is composed of three major functional block; a CPRB(combinational predecoder-reencoder block), RCB(register copy block) and DCB(detection and correction block). Fig. 1(a) is a basic cell of predecoder-Reencoder and the entire block of the SCEE decoder is shown in Fig. 1(b).

The binary encoded data is generated by the

encoder G(D). The additions in Figure 1 are modulo-2 and all binary sequences  $\cdots$ ,  $b_{-1}$ ,  $b_0$ ,  $b_1$ ,  $\cdots$  are represented as power series  $b(D) = \cdots + b_{-1}D^{-1} + b_0 + b_1 + \cdots$ . The encoder has generator polynomials  $G_H(D)$  and  $G_L(D)$ .

Fig. 1(a) Predecoder-Reencoder and its basic cell

Fig. 1(b) SCEE decoder

In general, the encoder outputs are  $X(D)G_H(D)$  and  $X(D)G_L(D)$ . The control signal or syndrome C(D) only depends on channel errors, i.e., not on the data sequence X(D). And the SCEE decoder operates as follows:

1) The received data R(D) which may include errors in the transmissin channel are decoded by the CPRB which is made up of four predecoder and two reencoder.

- a) These main predecoded data U(D) are reencoded by the same encoder used at the transmission side and reencoded data V(D) is compared to the received data R(D) in the modulo-2 addition and OR-operation.

- b) Concurrently, two input sequences of predecoder, high-bits  $R_H(D)$  and low-bits  $R_L(D)$ , are reencoded by reencoder. And then this output data is compared to the received in the modulo-2 addition and OR-operation.

- 2) The output data V(D) of CPRB is input into the DCB. In the DCB, if the received data is equal to the output of the reencoder then control signals, J1 and J2, are both zero, but not when channel errors occur. And if a control signal or both one, J1 or/and J2, in the SCEE decoder is nonzero, we can predict erroneous bit positions. Then DCB finds the error-position and selects the erroneous data exactly by control signals in the SCEE decoder.

- 3) RCB stores the previous state of the predecoder and reencoder when error is detected.

The mathematical expression of the decoding procedure in the SCEE decoder shown in Figure 1 and Figure 2 can be explained as follows. At first, for R = 1/2, K = 7 convolutional encoder, we define that the encoded sequence Y(D) and generator matrix G(D) can be expressed as

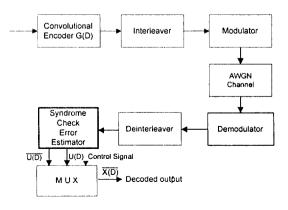

Fig. 2 Channel structure with the SCEE decoder

$$X(D) = x_0 + x_1 D + x_2 D^2 + \cdots$$

(1)

$$G(D) = {G_H(D) \choose G_H(D)} = {1 + D + D^2 + D^3 + D^6 \choose 1 + D^2 + D^3 + D^5 + D^6}$$

(2)

$$Y(D) = X(D) \cdot G(D), \tag{3}$$

where X(D) is the source data which is due to the data encoding and transmission.

If the transmitted data Y(D) is passed through noisy channel, then the corrupted received signal R(D) with channel noise E(D) is

$$R(D) = {\binom{R_H(D)}{R_L(D)}} = {\binom{Y_H(D) + E_H(D)}{Y_L(D) + E_H(D)}}$$

(4)

$$E(D) = {E_{II}(D) \choose E_L(D)}$$

$$= {e_{h0} + e_{h1}D + \dots + e_{hk}D^{k-1} + \dots \choose e_{lh} + e_{l1}D + \dots + e_{lk}D^{k-1} + \dots},$$

(5)

and the R(D) pass through predecoder, having

$$U(D) = r_{h,k} + r_{h,k-1} + \dots + r_{h,k-4} + r_{l,k-2} + r_{l,k-4}$$

=  $r_k + (e_{h,k} + e_{h,k-1} + \dots + e_{h,k-4} + e_{l,k-2} + e_{l,k-4}), (6)$

where D(D) is predecoded data and for the solution of previous equation (6), at first the predecoder outputs can be reexpressed in equation (7) by using SCEE decoding algorithm.

$$U(D) = R(D) \cdot G^{-1}(D)$$

$$= X(D) \cdot E^{*}(D).$$

(7)

where

$$E^*(D) = E(D) \cdot G^{-1}(D),$$

(8)

and  $E^*(D)$  equals the first order extension of error in SCEE decoder and  $G^{-1}(D)$  is the inverse of generator matrix. In relation between the predecoded output U(D) and channel error E(D) the channel error E(D) is extended to the first order convolutional error  $E^*(D)$  after predecoding  $E(D) \cdot G^{-1}(D)$ . And after the

predecoded output is passed through the reencoder G(D) its output, reencoded data V(D), is as follows.

$$V(D) = Y(D) + E^{**}(D),$$

(9)

where

$$E^{**}(D) = E^{*}(D) \cdot G(D),$$

(10)

and  $E^{**}(D)$  is the second order extension of error in the SCEE decoder. In the input of DCB, if the received data include channel errors, by the operation of control signal logic its output C(D) is erroneous terms remained only as shown in equation (11).

$$C(D) = R(D) + V(D)$$

=  $E(D) + E^{**}(D)$ . (11)

Here we define deterministic values,  $C_H(D)$  and  $C_L(D)$ , for proposed decoding algorithm. They are each defined as a bit sequence passed through high or low columns of predecoding matrix respectively and can be expressed as

$$C_H(D^i) \stackrel{\triangle}{=} (R_H(D^i) \cdot G_H^{-1}(D)) \cdot G_H(D)$$

$$C_L(D^i) \stackrel{\triangle}{=} (R_L(D^i) \cdot G_L^{-1}(D)) \cdot G_L(D)$$

(12)

Then, by following rule the major decoding operation of the SCEE decoder is performed.

Algorithm 1] Detection & Correction;

EKSE  $U(D^i) = X(D^i)$ .

{IF

$$C(D^i)$$

, THEN

{IF  $R_H(D^i) \cdot G_H^{-1}(D) := X(D^i)$ ,

THEN  $C_H(D^i) = X(D^i) \cdot G_H(D)$

ELSE IF  $R_L(D^i) \cdot G_L^{-1}(D) := X(D^i)$ ,

THEN  $C_L(D^i) = X(D^i) \cdot G_L(D)$

ELSE decoder failure,

THEN

$X(D^i) = U(D^i) = X(D^i) + E^*(D)$ }

Also, the outputs of the SCEE decoder passed through the CPRB, RCB and DCB are as followin equation (13).

$$\overline{X(D)} = \begin{cases} \frac{U(D) \text{ if no error}}{U(D) \text{ otherwise}} \end{cases}$$

(13)

where

$$U(D) = C_H(D) \ MUX \ C_L(D), \tag{14}$$

and  $\widehat{U(D)}$  is the corrected or detected output only if error exists and MUX is the selector operated by control signal.

Consequently, by syndrome check signals or control signals, J1 and J2, we can predict an error position or error-free and their relative outputs can be expressed in the equation (13) and (14). It should be clear that this form of decoder is capable of operation at very high speeds. Furthermore, by interleaving to appropriate depth, burst error correction at high speeds is quite feasible.

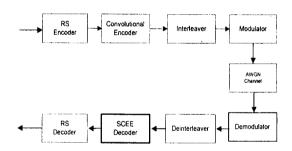

#### B. Concatenated SCEE/RS Coding Scheme

Concatenated coding can be used to obtain a small error rate with overall encoder/decoder implementation complexity which is less than would be required by a single coding operation. Classically, concatenation has consisted in cascading a block code and a convolutional code in a serial structure. In particular, the concatenated Viterbi/RS coding systems offer excellent performance. However, the decoding operation at extremely higher data rates is not currently feasible because of the difficulty of implementing the very high-speed Viterbi decoder and the large number of errors which must be corrected by the RS decoder[16] [17]. Against this background, this paper propose a new concatenated coding scheme with low complexity SCEE scheme for wireless communication systems. The proposed SCEE scheme is very powerful for ranodom errors but weak for burst errors. Since it is operated by two control signals and each state of control signals can not be expressed, all error patterns occurred in the constraint length of the predecoder. Therefore, our proposed decoder has the detection capability of burst errors, but doesn't have the correction, occurred in the constraint length of the predecoder.

Thus, we propose a concatenated SCEE/RS coding scheme which has a extremely powerful coding gain because of concatenation of our proposed SCEE and RS decoder with higher coding gain in burst error channel. The SCEE decoder provides satisfactory inner codes for the concatenated scheme. A block diagram of the concatenated SCEE/RS decoding scheme is shown in Fig. 3.

Fig. 3 Block diagram of the concatenated SCEE/RS coding scheme

# N. Simulation Results

#### A. Performance of the SCEE Decoder

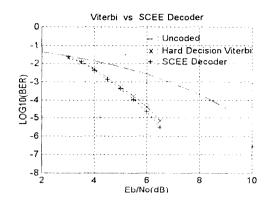

Figure 4 shows the simulated  $P_e$  (BER: bit error rate) performance after the SCEE decoding of the data sequence passed through AWGN channel when the R = 1/2 and K = 7 convolutional code is used for its encoding. Computer simulation is performed by the convolutional encoder/SCEE decoder scheme with BPSK and AWGN channel in SPW(Signal Processing Worksystem) tool.

As shown in figure 4, the  $P_e$  performance of the SCEE decoder is almost the same as the conventional Viterbi decoder adopted hard decision in the low received power, but according to the power increa-

Fig. 4 Pe performance of the SCEE decoder

sement it is better than the hard decision Viterbi decoder. This is because the error propagation of the Viterbi decoder for the incorrected bits depend on the constraint length K of the convolutional encoder. On the contrary, the SCEE decoder depends on the predecoder. In general the constraint length of convolutional encoder is longer than its inverse circuit[4]-[6]. Thus, the SCEE decoder has a good performance in the low variance region or high received power. Also, it has a extremely very low complexity as shown earlier.

# B. Performance of the SCEE/RS Decoder

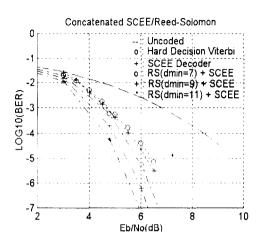

The concatenated SCEE/RS coding scheme can be easily implemented in very high speed applications. Also, the only significant reduction in hardware complexity occurs when the proposed coding techniques are employed. The achievable coding gains of the proposed decoder are 2.3dB, 2.6dB and 2.9dB with minimum distance 7, 9 and 11 respectively in BER =  $10^{-3}$ , but Reed Solomon codes have coding gains about 1.3dB and the hard decision Viterbi decoder has about 2.1dB.

As shown in Figure 5 and Table 1, according to the BER decreasing, coding gains are increased. Especially, then the concatenated SCEE/RS decoder is increased higher than the others. This means that the

Fig. 5 P<sub>c</sub> performance of the concatenated SCEE/RS coding

Table 1.  $P_c$  performace of the concatenated SCEE/RS coding

| BER                                                          | Coding Gain |        |

|--------------------------------------------------------------|-------------|--------|

|                                                              | 10 - 3      | 10 5   |

| Hard Decision Viterbi Decoder (K = 7, R = 1/2)               | 2.1 dB      | 3.2 dB |

| Soft Decision Viterbi Decoder (K = 7, R = 1/2, Level = 3bit) | 4.0 dB      | 5.3 dB |

| Reed-Solomon Decoder<br>(dmin = 11, k = 40, n = 50, GF(256)) | 1.3 dB      | 3.3 dB |

| SCEE Decoder( $K = 7$ , $R = 1/2$ )                          | 2.2 dB      | 3.4 dB |

| Concatenated SCEE/RS Decoder                                 | 2.9 dB      | 4.5 dB |

concatenated SCEE/RS coding scheme can be used as like the Viterbi decoder while Reed-Solomon codes are scarcely used in low power wireless communications. Also, the complexity of the proposed scheme is almost the same as the RS decoder.

#### V. Conclusion

We proposed a new decoding method, called SCEE, using the maximum convolutional effect. The proposed SCEE decoder is very powerful for random errors but weak for burst errors. Since it is operated by two control signals and each state of control signals can not be expressed, all error patterns occurred in the constraint length of the predecoder. Therefore, we proposed the concatenated SCEE/RS coding scheme which has a extrimely powerful coding gain because of the concatenation of our SCEE decoder and RS decoder with higher coding gains in burst error channel.

The computer simulation results of the proposed SCEE decoder and SCEE/RS coding scheme show that the computational complexity of the proposed SCEE decoder is significantly reduced compared with that of the conventional Viterbi decoder without degradation  $P_e$  performance. In addition, The proposed algorithm is easily implemented in very high speed applications and have higher coding gains in almost the same complexity with RS decoder. This means that the concatenated SCEE/RS coding scheme can be used like the Viterbi decoder while Reed-Solomon codes are scarcely used in low power wireless communications.

# VI. Acknowledgements

This work was supported by Korea Telecomm. (#97-31) and Ministry of Trade, Industry & Energy.

# 참고문헌

- S.Lin and D.J Costello Jr, Error Control Coding. Fundamental and Application. Pretice-Hall 1983.

- S.B. Wicker, Error Control Systems for Digital Communication and Storage. Pretice-Hall, 1995.

- G. D. Forney Jr. "The Viterbi Algorithm," Proc. IEEE, vol 61, pp 268-279, Mar. 1973.

- S. Kubota, S. Kato, T.Ishitani "Novel Viterbi Decoder-VLSI Implementation and Its Performance," *IEEE Trans. Commun.* vol 41. No.8 pp 1169-1178, Aug. 1993.

- 5. K. Seki, S. Kubota, M. Mizoguchi and S. Kato

- "Very Low Power Consumption Viterbi Decoder LSIC Employing the SST(scarce state transition) Scheme for Multimedia Mobile Communications," Electron. Lett., vol. 30, no. 8 pp. 637-638, Apr. 1994.

- S. Ping, Y, Yan, and C. Feng, "An Effective Simplifying Scheme for Viterbi Decoder," *IEEE Trans. Commun.* vol. 39, No 1, Jan. 1991.

- J.Pieter M. Schalkwijk, and A.J.Vinck, "Syndrome DeCoding if Binary Rate-1/2 Convolutional Codes," *IEEE Trans. Commun.*, vol. Com-24, pp 977-985, Sept. 1976.

- G. Fettweis and H. Meyr, "Parallel Viterbi Algorithm Implementation: Breaking the ACS-bottleneck," *IEEE Trans. Commun.*, vol. 37, pp785-790, August 1989.

- J. A. Heller and I. M. Jacobs, "Viterbi Decoding for Satellite and Space Communication," *IEEE Trans. Commun.*, Technol., vol. COM-19, no. 5, pp 835-848, Oct. 1971.

- J. Joeressen, M. Vaupel and H. Meyr, "High-Speed VLSI Architectures for Soft-Output Viterbi Decoding," Journal of VLSI Signal Processing Aug. pp. 169-181, 1994.

- S. W. Kim, "Error Control Codes for Digital Recoding Systems," *IEEE Trans. Consumer Ele*ctronics, vol 35, No. 4 pp 907-916, Nov. 1993.

- Charles. M. Rader, "Memory Management in a Viterbi Decoder," *IEEE Trans. Commun.* vol COM-29, No. 9, pp 1399-1401, Sep. 1981.

- A. J. Viterbi, "Convolutional Codes and Their Performance in Communication systems," *IEEE Trans. Commun.* vol. COM-19, pp 751-772, 1981.

- 14. E. R. Berlekamp, R. E. Peile, S. P. Pope, "The Application of Error Control to Communications," *IEEE Commun. Magazine*. vol. 25, No. 4, pp 44-57, Apr. 1987.

- Seungbae. choi, Moon Ho Lee, "High Speed Pattern Matching for a fast Huffman Decoder," *IEEE Trans. Consumer Elect.* vol.41, no.1, 1995.

- 16. Moon Ho Lee, Seungbae. Choi, Jinsu Chang, "A

- High Speed Reed-Solomon Decoder," IEEE, VLSI Signal processing Workshop(osaka), Oct 16-18, 1995.

- Moon Ho Lee, Seungbae. Choi, Jinsu. Chang, "A High Speed Reed-Solomon Decoder," *IEEE Trans. Consumer Elect.*, vol.41, no.4, Nov. 1995.

- Jinsu. Chang, Moon Ho Lee "A High Speed Viterbi Decoder", ICEIC'95(China) Aug 7-12, pp 364-367, 1995.

- Jinsu Chang, Seungbae. Choi, Juyong Park, Moon Ho Lee, "A Syndrome Check Error Estimation Algorithm for Convolutional Coding," The 2nd Inter. workshop. on. Multi-Dimentional Mobile Communication. pp 556-560, July 18-20, 1996. (MDMC'96)

- Seungbae Choi, Jinsu Chang, Juyong Park, Moon Ho Lee, "A New Decoding Algorithm for Convolutional Encoding Using Syndrome Checking Error Estimation," *IEEE ICCS/ISPACS* '96, Singapore, Nov. 25-29, 1996.

- Jinsu Chang, Seungbae Choi, Moon Ho Lee, "A Low Complexity SCEE Algorithm for Convolutional Codes and Its Concatenated Coding for Wireless Communication," Accepted for IEEE ICUPC'97, Sandiego, Oct 12-16, 1997.

장 진 수(Jin Su Chang) 정회원 1996년 2월:전북대학교 정보통 신공학과 졸업(공학 사)

1996년 3월~현재:전북대학교 대학원 정보통신공학과 석사과정 재학중

※관심분야: Modulation, Channel coding

최 승 배(Seung Bae Choi) 정회원 1993년 2월:전북대학교 정보통 신공학과 졸업(공학 사)

1996년 2월:전북대학교 대학원 정보통신공학과 졸업 (공학석사)

1996년 3월~현재:전북대학교 대

학원 컴퓨터공학과 박사과정 재학중 ※관심분야: Channel coding, Modulation

이 문 호(Moon Ho Lee) 정회원 1970년~1980년:남양문화방송(주) 송신소장

1985년 8월~1986년 8월:미국 미 네소타주립대 전기 과 포스터닥터

1995년 12월~1996년 12월:독일 하노버 아혼공대 전

\*기과 연구교수 박사, 통신기술사

※일본동경대학 정보통신공학박사, 통신기술사 ※현재:전북대 정보통신공학과 교수 ※관심분야:디지털 이동통신, 영상통신, 무선 ATM 네트워크