논문 99-24-4B-3

# 입력큐를 갖는 ATM 교환기에서 결합우선 순위제어의 성능분석

정회원 이 계 상\*

## Performance Analysis of a Combined Priority Control for Input Queueing ATM Switches

Kye Sang Lee\* Regular Member

요 약

최근 들어 입력 큐를 갖는 ATM 교환기의 중요성이 높아지고 있음에도 불구하고, 이들에 공간 및 시간 우선순 위 제어의 결합 방식이 적용된 경우에 대한 성능 연구는 부족하다. 본 논문에서는 높은 서비스 품질과 낮은 서비 스 품질을 요구하는 두 개 트래픽 클래스를 가정하여, ATM 교환기의 입력 큐에 공간 우선순위 제어로서 버퍼 부 분 공유 방식과 시간 우선순위 제어로서 상태의존 스케쥴링 방식이 함께 적용된 결합 제어 방식에 대한 성능을 분 석한다. 분석은 세미 마코프 프로세스 개념을 이용하여 두 단계로 이루어진다. 분석 결과로서, 여러 가지 시스템 변수가 교환기 성능에 미치는 영향을 살펴본다. 특히, 버퍼 부분 공유 방식의 문턱 값과 스케쥴링 방식의 스케쥴링 변수가 두 트래픽 클래스의 서비스 품질에 미치는 영향을 보이고, 아울러 이 들 두 변수를 적절히 조정함으로써 넓은 폭의 요구 서비스 품질 차이를 갖는 두 개 트래픽 클래스에 대해 허용 입력 부하를 최대화 할 수 있음을 보 있다.

#### ABSTRACT

In spite of growing importance of input queueing ATM switches, there have been little research on performance of input queues, of ATM switches, to which combined priority controls of space and time priority schemes are applied. In this paper, assuming two classes of traffics requiring high and low quality-of-service (QoS), we analyze a combined priority control method of partial buffer sharing and general state-dependent scheduling schemes in the input queues of a nonblocking asynchronous transfer mode (ATM) switch. The analysis is done in two steps, using a semi-Markov process concept. As results, we show how various system parameters affect the performances. Particularly, we show how the threshold value and the scheduling parameter of the combined scheme can affect dynamically the performance differences between the two classes. We further show how we can adjust the threshold and the scheduling parameter against a wide range of QoS gaps between the two classes to maximize the admissible load.

### I. Introduction

The asynchronous transfer mode (ATM) will be the basic transmission and switching paradigm, on which the emerging next generation multimedia LANs and the future broadband integrated services digital networks (B-ISDN) are to be constructed [1,2]. In ATM networks, all traffics are segmented into small fixed-size packets called cells and transferred via a series of ATM switches. Generally, packet streams from diverse applications require different packet loss and delay

<sup>\*</sup> 동의대학교 전자통신공학과(ksl@hyomin.dongeui.ac.kr) 논문번호: 98254-0619, 접수일자: 1998년 6월 19일

constraints, or different quality of services (QOSs) in short. At the same time, ATM networks are required to be utilized as fully as possible. Thus, in order to increase the utilization of ATM networks while meeting the different QOSs, appropriate priority control schemes are needed at various points in ATM networks, particularly buffers in ATM switches.

Many researchers have investigated performances of priority control schemes applied (or which can be applied) to the output queues of a nonblocking ATM switch. For example, various time or space priority schemes<sup>[3,4,5]</sup> studied in a single queue (or an ATM multiplxer model) can be applied to the output queues of ATM switches. Recently, Cheng and Akyildiz analyzed a single finite queue with a controlled push-out scheme and a general state-dependent service discipline<sup>[6]</sup>. Using a general service discipline they were able to model several function. different service disciplines such as head-of-line (HOL), shortest line first. Their work was also motivated by the performance study of an output queue of an ATM switch.

Meanwhile, only a few studies have been done on the priority schemes in the input queues of a nonblocking ATM switch. Chen and Guérin analyzed the performance of a two-priority input queueing switch in which only time priority was considered<sup>[7]</sup>. They obtained the saturation throughput of low priority class in a preemptive HOL scheduling scheme, assuming that the speed-up factor of the switch is equal to 1. Gupta and Georganas analyzed two non-preemptive time priority schemes for an input queueing packet switch<sup>[8]</sup>. They obtained mean delays of two priority classes, also assuming the speed-up factor of 1.

As seen from the above, while most of studies are restricted to the output queues of switches, relatively few studies have been done for the input queues of switches. Moreover, there have been fewer studies on the combined space and time priority schemes for the input queueing switches. In order to deal with QoSs by using

input queueing ATM switches which are less complex in hardware than output queueing switches, however, understanding the performances of a variety of combined priority schemes for the input queues of ATM switches is essential.

In this paper, we study input queues of a nonlocking ATM switch assuming two classes of traffic (high and low QoS guaranteed ones). To each input queue, we apply a combined priority control scheme: the partial buffer sharing scheme for space priority control and the general state-dependent scheduling scheme for priority control. The speed-up factor of the switch is allowed to be greater than 1 in our switch model. The analysis is carried out in the discrete-time domain, using the semi-Markov process (SMP) concept. In numerical results, we show how packet loss probabilities and mean waiting times of two classes of traffic change with various system parameters such as speed-up factor, buffer size, threshold, and scheduling parameter. Particularly, we show how threshold value and the scheduling parameter of the combined scheme affect dynamically the performance differences between the two classes. This implies that by using the combined method of the two priority control schemes, we can control flexibly the performances of the input queueing ATM switch. Also, we show that for a wide range of QoS gap of the two classes of traffic, we can maximize the admissible load, by adjusting the threshold and the scheduling parameter.

This paper is organized as follows. In Section 2, following this introduction, we describe the system model in detail. In Section 3, we analyze the system. In Section 4, we show some typical numerical examples. Finally, we shall have concluding remarks in Section 5.

## II. System Description

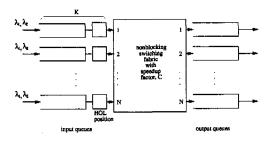

We consider a class of ATM switches as shown in Fig. 1. The switch consists of N input queues, N output queues and nonblocking

switching fabrics inbetween. We assume that the switch operates synchronously with fixed-size packets. During each fixed-time interval called a slot, every input(output) can receive(transmit) one packet. We assume that each input queue has buffer spaces of K packets including the HOL position. The internal speed of the switching fabrics is assumed to be C times faster than that of the input (or the output) link. In other words, up to C packets, among the packets at the HOL position having the same destination, can go through the switching fabrics to the destination output during a single slot. For this reason, C is referred to as the speed-up factor. In this paper, assuming two classes of input traffic, we concentrate on the performance of the input queue to which we apply a combined priority control of the partial buffer sharing scheme and the general state-dependent scheduling scheme and a HOL packet contention priority scheme.

Fig. 1. System model.

We assume that packets arrive at the N input queues according to independent and identical Bernoulli processes with probability  $\lambda$ , and that an arriving packet is either a class 1 packet with probability r or a class 2 one with probability 1 -r. Thus, class 1 and 2 traffics become also Bernoullis, and the probabilities of class 1 and 2 packet arrivals at each input queue are then equal to

$$\lambda_1 = r\lambda$$

and  $\lambda_2 = (1-r)\lambda$ , (1)

respectively. We will refer to r as the traffic mix ratio. We assume that the class 1 and 2 traffic require the high and low QoS guarantees, respectively. We also assume that packets are

uniformly distributed among all outputs and successive packets are independently destined from those of previous arrivals.

Now, we describe the partial buffer sharing scheme. An arriving class 1 packet can always enter the queue, as long as it finds at least a buffer space in the queue. On the other hand, a class 2 packet can enter the queue, only if it finds the queue filled with less than T packets excluding one in the HOL position. Otherwise, it is lost. The threshold T has an integer value between zero and K-1.

Next, we describe the general state-dependent scheduling scheme. First, the class of a packet to be scheduled (i.e., moved into the HOL position) next is determined by the scheduling functions,  $a_c(i,j)$ , c=1,2 which is defined as the probability that class c will be selected, given that there are i class 1 and j class 2 packets in the queue. Then, one packet belonging to the selected class is moved into the HOL position on a FIFO basis. Obviously, we should have  $a_2(i,j) = 1$  for i+j > 0. And to ensure that the HOL position will not be empty as long as there are some packets in the queue, we assume that  $a_1(i,0) = 1 \text{ for } i > 0, \text{ and } a_2(0,j) = 1$ for j > 0. a, we can model various scheduling schemes. The following are just two examples among those, which are used in computing numerical results in this paper:

- i) Head of Line (HOL) Scheduling  $\alpha_1(i,j) = 1$  if i > 0.

- ii) Bernoulli Selection (BS) Scheduling  $a_1(i, j) = p$  if i > 0 and j > 0.

Under the HOL scheme, a class 1 packet is scheduled, if any, irrespective of the presence of class 2 packets. Therefore, among all possible schemes using  $\alpha$  the HOL scheme is considered to give the highest time-priority to class 1 traffic. Under the BS scheme, a class 1 packet will be scheduled with probability p and a class 2 packet with probability 1-p. In the BS schemes, according to the value p, the amount of time priority

divided between class 1 and 2 varies. Note that when p=1, the BS scheme becomes equivalent to the HOL scheme.

Lastly, we assume higher priority to the class 1 over 2 in the HOL packet contention. In other words, when more than C packets at the HOL position contend for the same output, class 1 packets are selected for transmission before class 2 packets. In addition, packet selections within each class are assumed to be done randomly.

## III. Performance Analysis

In this section, we analyze the input queue model described in Section 2, following two steps: virtual HOL queue analysis in the first step and input queue analysis in the second step. Here, we assume that the size, N, of the switch goes to infinity.

#### 1. Virtual HOL Queue Analysis

We consider virtual queues consisting of the HOL packets heading for the same output port. In the limit of  $N\rightarrow\infty$ , the virtual queues become mutually independent, since the packet arrival processes at different virtual queues become mutually independent in the limit<sup>(9)</sup>.

We tag a virtual queue among those. Note that the delay of a packet in the tagged virtual queue is the HOL contention time in the input queue. Let  $P_{II}$  and  $P_{I2}$  be the steady-state loss probabilities of class 1 and 2 packets at the input queue, respectively. Then, we can approximate the numbers of class 1 and 2 packets arriving at the virtual queue during a slot time as having Poisson distributions with effective rates

$$\lambda_1 = \lambda_1 (1 - P_A) \text{ and } \lambda_2 = \lambda_2 (1 - P_B), \tag{2}$$

respectively. This assumption has already been used with single priority switches  $^{[9,10]}$  for which the arrival processes at virtual queues can be shown to in fact tend toward a Poisson distribution as  $N\rightarrow\infty$ . Similar Poisson approximations have also been used for two priority switches  $^{[7,8]}$ . From the HOL packet contention

assumed in Section 2, the virtual HOL queue can be modelled as having C number of servers with deterministic service time (= one slot) and such a service discipline that class 1 packets are served before class 2 packets and in random order among the same class packets. We will find the delay distributions of each class packet in this virtual queue.

Let  $I_n$  and  $J_n$  be the numbers of class 1 and class 2 packets, respectively, in the virtual queue immediately after the end of n-th slot. We assume that selection of packets for transmission is made immediately after new packet arrivals at the queue at the beginning of a slot. Then,  $\{(I_n, J_n), n=1,2,...\}$  constitutes a Markov chain. Let  $h_{(i_n,j_n):(k_n,j_n)}$  be the state transition probability of the chain. Also, let  $a_n$  and  $b_n$  denote the probabilitis that n packets arrive at the virtual queue during one slot time for class 1 and 2 traffic, respectively. Equivalently,

$$a_n \triangleq e^{-\lambda_1} (\lambda_1)^n / n!$$

and  $b_n \triangleq e^{-\lambda_2} (\lambda_2)^n / n$  (3)

for  $n \ge 0$ . Then, the state transition probabilities  $h_{(i,j):(k,l)}$  can be obtained as follows:

#### (a) For $i + j \le C$ and i < C,

$$h_{(i,j):(k,l)} = \begin{cases} \sum_{m=0}^{C-(i+j)} \sum_{n=0}^{m} a_n b_{m-n}, & \text{for } k = 0 \text{ and } l = 0, \\ \sum_{m=0}^{C+l-(i+j)} a_n b_{C+l-(i+j+n)}, & \text{for } k = 0 \text{ and } 0 < l < j, \\ \sum_{n=0}^{C-i} a_n b_{C+l-(i+j+n)}, & \text{for } k = 0 \text{ and } l \ge j, \\ 0, & \text{for } k > 0 \text{ and } 0 \le l < j, \\ a_{k+C-i} b_{l-j}, & \text{for } k > 0 \text{ and } l \ge j. \end{cases}$$

$$(4)$$

## (b) For i+j > C and i < C,

$$h_{(i,j):(k,l)} \ = \ \begin{cases} \sum_{n=0}^{C+l-(i+j)} a_n b_{C+l-(i+j+n)}, & \text{for } k=0 \text{ and } i+j-C \le l < j. \\ \sum_{n=0}^{C-i} a_n b_{C+l-(i+j+n)}, & \text{for } k=0 \text{ and } l \ge j, \\ a_{k+C-i} b_{l-j}, & \text{for } k>0 \text{ and } l \ge j, \\ 0, & \text{otherwise.} \end{cases}$$

(5)

(c) For  $i+j \ge C$  and  $i \ge C$ ,

$$h_{(i,j):(k,l)} = \begin{cases} a_{k-(i-C)}b_{l-j}, & \text{for } k \geq i-C \text{ and } l \geq j, \\ 0, & \text{otherwise.} \end{cases}$$

(6)

This completes the state transition matrix of the chain defined by  $\mathbf{H} \triangleq [h_{(i,i):(k,b)}]$ . Let  $\psi_{i,j}$  be the steady-state probability that there are i class 1 and j class 2 packets in the virtual queue. Further, define  $\Psi_i \triangleq (\psi_{i,0}, \psi_{i,1}, \dots)$  for  $i \geq 0$  and  $\Psi \triangleq (\Psi_0, \Psi_1, \dots)$ . Then, from  $\Psi = \Psi \mathbf{H}$  and  $\sum_i \sum_j \psi_{i,j} = 1$ , we can compute  $\psi_{i,j}$  for  $i \geq 0$  and  $j \geq 0$ . In the numerical computation, we need to truncate the state space.

Now, we derive the delay distribution of class 1 packets in the virtual queue. Consider a tagged class 1 packet and let  $S_I$  be the delay of the tagged packet in the virtual queue. Note that since the high priority in the contention is given to class 1 packets, the delay of the tagged class 1 packet is not affected by the presence of class 2 packets. Let  $P_{m,k}$  denote the probability that the remaining delay is m time slots until the tagged class 1 packet completes the service, on the condition that there are k class 1 packets including itself in the queue immediately after the arrival instant in a given time slot. Then,  $P_{m,k}$  for  $k \ge 1$  and  $m \ge 1$  can be obtained as follows:

$$P_{m,k} = \begin{cases} 1, & \text{for } 1 \le k \le C \text{ and } m = 1, \\ 0, & \text{for } 1 \le k \le C \text{ and } m \ge 2, \\ \frac{C}{k}, & \text{for } k > C \text{ and } m = 1, \\ \frac{k - C}{k} \sum_{j=0}^{\infty} P_{m-1,k-C+j} \frac{e^{-\lambda_1^j} (\lambda_1^j)^j}{j!}, & \text{for } k > C \text{ and } m \ge 2. \end{cases}$$

(7)

We can calculate  $P_{m,k}$  for  $m \ge 2$  by recursion on m. Let  $s_l(m)$  be the probability that the delay of the tagged class 1 packet,  $S_l$  is equal to m slots. Then,  $s_l(m)$  is obtained from

$$s_1(m) = \sum_{k=1}^{\infty} P_{m,k} \sum_{i=0}^{k-1} \psi_i \frac{e^{-\lambda_1'} (\lambda_1')^{k-i-1}}{(k-i-1)!},$$

(8)

for  $m \ge 1$  where  $\phi_i = \sum_{j=0}^{\infty} \phi_{i,j}$  for  $i \ge 0$ .

Similarly, we derive the delay distribution of class 2 packets in the virtual queue. Consider a tagged class 2 packet and let  $S_2$  be the delay of the tagged packet in the virtual queue. Let  $Q_{m,l,k}$  denote the probability that the remaining delay is m time slots until the tagged packet completes the service, on the condition that there are l class 2 packets including the tagged one and k class 1 packets in the queue immediately after the arrival instant in a given time slot. Then,  $Q_{m,l,k}$  for  $m \ge 1$ ,  $l \ge 1$ , and  $k \ge 0$  can be obtained as follows: (a) For m=1,

$$Q_{1,l,k} = \begin{cases} 1, & \text{for } l+k \le C, \\ \frac{C-k}{l}, & \text{for } l+k > C \text{ and } k < C, \\ 0, & \text{for } l+k > C \text{ and } k \ge C. \end{cases}$$

(9)

(b) For  $m \ge 2$ ,

$$Q_{m,l,k} = \begin{cases} 0, & \text{for } l+k \leq C, \\ \frac{l-(C-k)}{l} \sum_{i=0}^{(m-1)C-1} \sum_{j=0}^{\infty} Q_{m-1,l-C+k+j,i} \frac{e^{-\lambda_1'}(\lambda_2')^i}{i!} \frac{e^{-\lambda_2'}(\lambda_2')^j}{j!}, \\ & \text{for } l+k > C \text{ and } k < C, \end{cases}$$

$$\sum_{i=0}^{mC-k-1} \sum_{j=0}^{\infty} Q_{m-1,l+j,k-C+i} \frac{e^{-\lambda_1'}(\lambda_1')^i}{i!} \frac{e^{-\lambda_2'}(\lambda_2')^j}{j!}, \\ & \text{for } l+k > C \text{ and } C \leq k < mC, \end{cases}$$

$$0, & \text{for } l+k > C \text{ and } k \geq mC.$$

$$(10)$$

We can calculate  $Q_{m,l,k}$  for  $m \ge 2$  by recursion on m. Let  $s_2(m)$  be the probability that the delay of the taggged class 2 packet,  $S_2$ , is equal to m slots. Then for  $m \ge 1$ , we have

$$s_2(m) = \sum_{i=1}^{\infty} \sum_{k=0}^{mC-1} Q_{m,l,k} \cdot \text{Prob} \begin{bmatrix} \text{there are } l \text{ class 2 packets including the tagged one} \\ \text{and } k \text{ class 1 packets in the queue immediately after} \end{bmatrix}$$

$$= \sum_{i=1}^{\infty} \sum_{k=0}^{mC-1} Q_{m,l,k} \sum_{i=0}^{k} \sum_{j=0}^{l-1} \psi_{i,j} \frac{e^{-\lambda_i^t} (\lambda_i^t)^{k-i}}{(k-i)!} \frac{e^{-\lambda_i^t} (\lambda_j^t)^{l-j-1}}{(l-j-1)!}.$$

(11)

#### Input Queue Analysis

Again, as the switch size goes to infinity, i.e.,  $N\rightarrow\infty$ , each input queue forms an independent queue. This follows directly from the fact that the virtual queue are mutually independent in the limit. Therefore, with the HOL contention time

distributions of each class packets, we can now separate each input queue from the switch, and model it as an independent  $Geom_1$ ,  $Geom_2/G_1$ ,  $G_2/1/K$  queue where the service time distributions of class 1 and class 2 packets are now  $s_1(m)$  and  $s_2(m)$ , respectively, obtained in the previous subsection.

Let  $K_n$  and  $L_n$  be the numbers of class 1 and class 2 packets, respectively, in the queue immediately after the n-th HOL packet departure. Then,  $\{(K_n, L_n), n=1,2,...\}$  constitutes a Markov chain. Let  $p_{(i,j):(k,l)}$  be the state transition probability of the chain. Before we obtain the transition probabilities, we define some notations. First, let  $N(k, l, \lambda_1, \lambda_2, s(m))$  denote the probability that k class 1 and l class 2 packets arrive during the service time of which the distribution function is s(m) in general. Then, we have

$$N(k,l,\lambda_1,\lambda_2,s(m)) = \sum_{m=k+l}^{\infty} \frac{m!}{k!l!(m-k-l)!} \lambda_1^k \lambda_2^l (1-\lambda_1-\lambda_2)^{m-k-l} s(m).$$

(12)

For example, we can express the probability that k class 1 and l class 2 packets arrive during a service time (i.e., a HOL contention time) of a class c (=1,2) packet as  $N(k, l, \lambda_1, \lambda_2, s_c(m))$ . Further, we define, conditioning that k class 1 and l class 2 packets arrive during a service time interval, the probability that exactly l'( $\leq l$ ) class 2 packet arrivals belong to the first T packet arrivals as P(k, l, T, l'). Then, we have

$$P(k,l,T,l') = \frac{\binom{T}{l'} \binom{k+l-T}{l-l'}}{\binom{k+l}{l}}.$$

(13)

Lastly, we use the following elementary functions for notational simplicity:

$$u(k) \stackrel{\triangle}{=} \left\{ \begin{array}{ll} 1, & \text{if } k \geq 0, \\ 0, & \text{otherwise}, \end{array} \right. \quad \text{and} \quad \delta(k) \stackrel{\triangle}{=} \left\{ \begin{array}{ll} 1, & \text{if } k = 0, \\ 0, & \text{otherwise}. \end{array} \right.$$

Then, using the above notations, the state transition probability  $p_{(i,j) : (k,j)}$  can be obtained as the following:

(a) For i=0 and j=0, a class 1(class 2) packet will arrive and be served next, with probability r (probability 1-r).

$$P_{(0,0):(k,l)} = \begin{cases} rN(k,l,\lambda_1,\lambda_2,s_1(m)) + (1-r)N(k,l,\lambda_1,\lambda_2,s_2(m)), & \text{for } k+l < T, \\ r\sum_{l'=l}^{\infty}N(k,l',\lambda_1,\lambda_2,s_1(m))P(k,l',T,l) + (1-r)\sum_{l'=l}^{\infty}N(k,l',\lambda_1,\lambda_2,s_2(m))P(k,l',T,l), \\ & \text{for } T \leq k+l < K-1 \text{ and } l \leq T, \end{cases}$$

$$r\sum_{k'=k}^{\infty}\sum_{l'=l}^{\infty}N(k',l',\lambda_1,\lambda_2,s_1(m))P(k',l',T,l), \\ +(1-r)\sum_{k'=k}^{\infty}\sum_{l'=l}^{\infty}N(k',l',\lambda_1,\lambda_2,s_2(m))P(k',l',T,l), \\ & \text{for } k+l = K-1 \text{ and } l \leq T. \end{cases}$$

$$(144)$$

(b) For  $0 < i \le T$  and j = 0, a class 1 packet will be served next. Hence, we have

$$P_{(i,0)(k,l)} = \begin{cases} u(k-(i-1))N(k-(i-1),l,\lambda_1,\lambda_2,s_1(m)), & \text{for } k+l < T, \\ u(T-(i-1)-l)\sum_{l'=i}^{\infty} N(k-(i-1),l',\lambda_1,\lambda_2,s_1(m))P(k-(i-1),l',T-(i-1),l), \\ & \text{for } T \le k+l < K-1 \text{ and } l \le T, \\ u(T-(i-1)-l)\sum_{l'=k-(i-1)}^{\infty} \sum_{l'=i}^{\infty} N(k',l',\lambda_1,\lambda_2,s_1(m))P(k',l',T-(i-1),l), \\ & \text{for } k+l = K-1 \text{ and } l \le T. \end{cases}$$

$$(15)$$

(c) For  $T < i \le K-1$  and j=0, also, a class 1 packet will be served next. However, we have a simpler equation in this case:

$$P_{(l,0):(k,l)} = \begin{cases} 0, & \text{for } k+l < T, \\ u(k-(i-1))\delta(l) \sum_{l'=0}^{\infty} N(k-(i-1).l', \lambda_1, \lambda_2, s_1(m)), \\ & \text{for } T \le k+l < K-1 \text{ and } l \le T. \end{cases}$$

$$\delta(l) \sum_{k'=k-(i-1)}^{\infty} \sum_{l'=0}^{\infty} N(k', l', \lambda_1, \lambda_2, s_1(m)), \\ & \text{for } k+l = K-1 \text{ and } l \le T. \end{cases}$$

$$(16)$$

(d) For i=0 and  $0 < j \le T$ , a class 2 packet will be served next. Hence, we have

$$P(0,j)(k,l) = \begin{cases} u(l-(j-1))N(k,l-(j-1),\lambda_1,\lambda_2,s_2(m)), & \text{for } k+l < T, \\ u(l-(j-1))\sum_{l'=l-(j-1)}^{\infty} N(k,l',\lambda_1,\lambda_2,s_2(m))P(k,l',T-(j-1),l-(j-1)), & \text{for } T \le k+l < K-1 \text{ and } l \le T. \\ u(l-(j-1))\sum_{k'=k}^{\infty} \sum_{l'=l-(j-1)}^{\infty} N(k',l',\lambda_1,\lambda_2,s_2(m))P(k',l',T-(j-1),l-(j-1)), & \text{for } k+l = K-1 \text{ and } l \le T. \end{cases}$$

$$(17)$$

(e) For i > 0, j > 0 and i+j ≤ T, a class 1(class

2) packet will be served next with probability a₁(i,j) (probability a₂(i,j)). Hence, we have

$$\begin{aligned} & \alpha_1(i,j) u(k-(i-1)) u(i-j) N(k-(i-1),i-j,\lambda_1,\lambda_2,s_1(m)) \\ & + \alpha_2(i,j) u(k-i) u(l-(j-1)) N(k-i,l-(j-1),\lambda_1,\lambda_2,s_2(m)), \\ & \text{for } k+l < T, \\ & \alpha_1(i,j) u(l-j) u(T-(i-1)-l) \\ & \cdot \sum_{l'=l-j}^{\infty} N(k-(i-1),l',\lambda_1,\lambda_2,s_1(m)) P(k-(i-1),l',T-(i+j-1),l-j) \\ & + \alpha_2(i,j) u(l-(j-1)) u(T-i-l) \\ & \cdot \sum_{l'=l-j}^{\infty} N(k-i,l',\lambda_1,\lambda_2,s_2(m)) P(k-i,l',T-(i+j-1),l-(j-1)), \\ & \text{for } T \le k+l < K-1 \text{ and } l \le T, \\ & \alpha_1(i,j) u(l-j) u(T-(i-1)-l) \\ & \cdot \sum_{l'=k-l-i-1}^{\infty} \sum_{l'=k-l-i-1}^{\infty} N(k',l',\lambda_1,\lambda_2,s_2(m)) P(k',l',T-(i+j-1),l-j) \\ & + \alpha_2(i,j) u(l-(j-1)) u(T-i-l) \\ & \cdot \sum_{k'=k-l-i-1}^{\infty} \sum_{l'=k-l-i-1}^{\infty} N(k',l',\lambda_1,\lambda_2,s_2(m)) P(k',l',T-(i+j-1),l-(j-1)), \\ & \text{for } k+l = K-1 \text{ and } l \le T. \end{aligned}$$

(f) For i > 0, j > 0,  $T < i+j \le K-1$  and  $j \le T$ , again a class 1(class 2) packet will be served next with probability  $\alpha_{1(i,j)}$  (probability  $\alpha_{2(i,j)}$ ) as in (e). However, we have a simpler form of equation in this case:

$$p_{(i,j):(k,l)} = \begin{cases} 0, & \text{for } k+l < T, \\ \alpha_1(i,j)u(k-(i-1))\delta(l-j) \sum_{l'=0}^{\infty} N(k-(i-1),l',\lambda_1,\lambda_2,s_1(m)) \\ +\alpha_2(i,j)u(k-i)\delta(l-(j-1)) \sum_{l'=0}^{\infty} N(k-i,l',\lambda_1,\lambda_2,s_2(m)), \\ & \text{for } T \le k+l < K-1 \text{ and } l \le T. \end{cases}$$

$$\alpha_1(i,j)\delta(l-j) \sum_{k'=k-l(i-1)}^{\infty} \sum_{l'=0}^{\infty} N(k',l',\lambda_1,\lambda_2,s_1(m)) \\ +\alpha_2(i,j)\delta(l-(j-1)) \sum_{k'=k-l}^{\infty} \sum_{l'=0}^{\infty} N(k',l',\lambda_1,\lambda_2,s_2(m)), \\ & \text{for } k+l = K-1 \text{ and } l \le T. \end{cases}$$

$$(19)$$

This completes the state transition matrix defined by  $P \triangleq [p_{(i,j):(k,j)}]$  Let  $\pi_{i,j}$  be the steady-state probability that there are i class 1 and j class 2 packets in the queue immediately after the departure of a HOL packet. Further, let  $\prod_{j} \triangleq (\pi_{0,j}, \pi_{1,j}, \ldots, \pi_{K-1-j,j})$  for  $0 \le j \le T$  and  $\prod \triangleq (\prod_0, \prod_1, \ldots, \prod_T)$ . Then, from  $\prod = \prod_i P$  and  $\sum_i \sum_j \pi_{i,j} = 1$ , we can compute  $\pi_{i,j}$  for  $0 \le i \le K-1$ .

We now construct an SMP (Refer to [11,12] for the basic concept) where the state remains at the same state as one immediately after the last HOL packet departure. It is straightforward to find the steady-state probability  $\bar{\pi}_{i,j}$  of the SMP. Let  $\eta_{i,j}$  denote the mean residence time (in slots) during which the SMP stays in the state (i,j). Then, we have

$$\eta_{i,j} = \begin{cases}

\frac{1}{\lambda} + r\bar{S}_1 + (1-r)\bar{S}_2, & \text{if } i = 0 \text{ and } j = 0, \\

\alpha_1(i,j)\bar{S}_1 + \alpha_2(i,j)\bar{S}_2, & \text{otherwise,}

\end{cases}$$

(20)

where  $\overline{S}_1 = \sum_{m=1}^{\infty} m S_1(m)$  and  $\overline{S}_2 = \sum_{m=1}^{\infty} m S_2(m)$ . Therefore, the steady-state probability,  $\overline{R}_{i,j}$ , in the SMP is obtained as

$$\bar{\pi}_{i,j} = \frac{\pi_{i,j}\eta_{i,j}}{\sum_{l=0}^{T} \sum_{k=0}^{K-1-l} \pi_{k,l}\eta_{k,l}},$$

for  $0 \le i \le K-1$ ,  $0 \le j \le T$ , and  $i+j \le K-1$ . (21)

Now, we tag a slot arbitrarily and observe the state, i.e., the numbers of class 1 and 2 packets in the queue except the HOL position immediately after the slot boundary. We want to calculate the state probability  $\phi_{k,l}$  at this arbitrarily tagged slot. Note that at the tagged slot, the state of the SMP will be one of (i,j) where  $0 \le i \le K-1$ ,  $0 \le j \le T$  and  $0 \le i+j \le K-1$ . These are mutually exclusive and altogether constitute a total event. Therefore, with the definition of  $\phi_{k,l}(i,j)$  as the probability that the state at the tagged slot will be (k,l), on the condition that the SMP is in the state (i,j), we can apply the total probability law, i.e.,

$$\phi_{k,l} = \sum_{j=0}^{T} \sum_{i=0}^{K-1-j} \phi_{k,l}(i,j)\bar{\pi}_{i,j}.$$

(22)

Thus, we should find  $\phi_{k,l}(i,j)$  to obtain  $\phi_{k,l}$ . Before we derive  $\phi_{k,l}(i,j)$ , we define some notations. Let  $\tilde{s}_{c(m)}$  be the probability that the elapsed service time at the tagged slot will be m, on the condition that the class c (=1,2) packet is served. Then, we have

$$\tilde{s}_c(m) = \frac{1}{\tilde{S}_c} \sum_{j=m+1}^{\infty} s_c(j), \text{ for } m = 0, 1, \dots$$

(23)

Also, let  $\widetilde{p}_{(i,h):(k,h)}$  be  $p_{(i,h):(k,h)}$  as in (14)-(19) calculated with  $\widetilde{s}_{c(m)}$  instead of  $s_{c(m)}$ , i.e.,

$\tilde{p}_{(i,j):(k,l)} \stackrel{\triangle}{=} p_{(i,j):(k,l)}|_{\text{with substitutions } s_c(m) = \hat{s}_c(m)} \text{ for } c=1,2.$ (24)

Then, since we do not include the packet in the HOL position in the definition of  $\phi_{k,i}$ , it is straightforward to note that for  $i\neq 0$  or  $j\neq 0$ ,

$$\phi_{k,l}(i,j) = \tilde{p}_{(i,j):(k,l)}.$$

(25)

To find  $\phi_{k,l}(0,0)$  defined as

$$\phi_{k,l}(0,0) \stackrel{\triangle}{=} \operatorname{Prob} \left[ (k,l) \text{ at tagged slot} \mid \operatorname{SMP in} (0,0) \right],$$

(26)

we again apply the total probability law, by further conditioning on whether the system is being idle or busy at the tagged slot (i.e., whether the HOL position is occupied by a packet or not at the tagged slot) to get

$$\phi_{k,l}(0,0) = \operatorname{Prob}\left[ (k,l) \text{ at tagged slot } | \operatorname{SMP in} (0,0), \operatorname{Idle} \right]$$

$$\cdot \operatorname{Prob}\left[ \operatorname{Idle} | \operatorname{SMP in} (0,0) \right]$$

$$+ \operatorname{Prob}\left[ (k,l) \text{ at tagged slot } | \operatorname{SMP in} (0,0), \operatorname{Busy} \right]$$

$$\cdot \operatorname{Prob}\left[ \operatorname{Busy} | \operatorname{SMP in} (0,0) \right]$$

(27)

where Prob[..|...] denotes the conditional probability. It is easy to find that

Prob [ Idle | SMP in

$$(0,0)$$

] =  $\frac{1/\lambda}{1/\lambda + r\overline{S}_1 + (1-r)\overline{S}_2}$ , (28)

Prob [ Busy | SMP in

$$(0,0)$$

] =  $\frac{r\tilde{S}_1 + (1-r)\tilde{S}_2}{1/\lambda + r\tilde{S}_1 + (1-r)\tilde{S}_2}$ , (29)

and

Prob [

$$(k, l)$$

at tagged slot | SMP in  $(0, 0)$ , Idle ]

$$= \begin{cases} 1, & \text{if } k = 0 \text{ and } l = 0, \\ 0, & \text{otherwise,} \end{cases}$$

(30)

Finally, with the same reasoning used when obtaining (25), we note that

Prob

$$[(k,l)$$

at tagged slot | SMP in  $(0,0)$ , Busy  $]$

$$= \hat{p}_{(0,0):(k,l)}. \tag{31}$$

From (27) together with (28)-(31), we can calculate  $\phi_{k}(0,0)$ .

Finally, we are ready to get loss probabilities. Since both class 1 and class 2 packet streams are Bernoulli, from the BASTA(Bernoulli Arrival Sees the Time Averages)<sup>[13]</sup>, we have

$$P_{l1} = \sum_{l=0}^{T} \phi_{K-1-l,l} \tag{32}$$

and

$$P_{l2} = \sum_{l=0}^{T} \sum_{k=T-l}^{K-1-l} \phi_{k,l}.$$

(33)

Recall that the above derivations are based on the assumption that the packet loss probabilities of the two classes are already known. This naturally suggests an iterative solution. Starting with zero loss probabilities, we can continue to update loss probabilities iteratively until they converge.

After the steady-state statistics have converged, we then find the mean waiting times of the two classes. Let  $W_c$  (c=1,2) be the overall mean waiting time of a class c packet in the input queue, including the waiting time in the HOL position. Then, from the Little's law, we obtain

$$W_1 = \frac{L_1}{\lambda_1(1 - P_{l_1})} + \bar{S}_1 - 1 \tag{34}$$

$$W_2 = \frac{L_2}{\lambda_2(1 - P_{l2})} + \bar{S}_2 - 1, \tag{35}$$

where  $L_{l}$  and  $L_{2}$  are mean numbers of packets of each class in the queue except the HOL position, i.e.,  $L_{1} = \sum_{k=0}^{K-1-T} k \sum_{l=0}^{T} \phi_{k,l} + \sum_{k=K-T}^{K-1} k \sum_{l=0}^{K-k-1} \phi_{k,l}$  and  $L_{2} = \sum_{l=0}^{T} \frac{1}{l-0} i \sum_{k=0}^{K-l-1} \phi_{k,l}$ .

#### IV. Numerical Results

In this section, we present some numerical results. Specific scheduling schemes used in this

section are the HOL scheduling scheme and the Bernoulli Scheduling(BS) scheme.

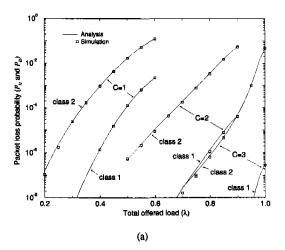

Fig. 2. Performances with varying speed-up factor C(=1,2,3) for K=10, T=5, HOL scheme and r=0.5. (a) Packet loss probabilities vs. total offered load  $\lambda$ . (b) Mean waiting times vs. total offered load  $\lambda$ .

The effect of increasing the speed-up factor of the switch are shown in Fig. 2 (a) and (b). With the speed-up factor C(=1,2,3) increasing, both performances are radically improved. With C=2 or 3, the performance can be improved significantly. This result agrees with previous ones obtained by other researchers. The speed-up factor can be regarded as the most influential factor affecting the overall performance among other system parameters. We have plotted the simulation results

together with the analytical ones for the verification purpose. In simulations, a switch model of 200 input ports was used.

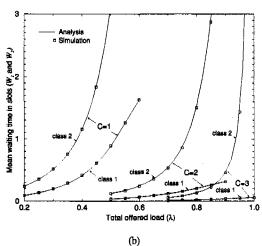

Fig. 3. Performances with varying buffer size K(=10,15,20,25) for C=2, T=8, HOL scheme, and r=0.5. Packet loss probabilities vs. total offered load  $\lambda$ .

Buffer size affects the loss performace only. In Fig. 3, as the buffer size increases, the loss probabilities of class 1 packets decrease resulting in the decrease of the average loss probabilities. In this figure, we used a fixed threshold T, resulting in no changes in curves of class 2 loss probabilities. We also observed that any noticeable effects were not shown on the mean waiting times with the buffer size. These facts suggest that as the buffer size increases, the admissible load can be increased accordingly due to the loss performance improvements, but confined eventually by the mean waiting time performance.

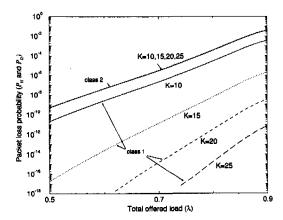

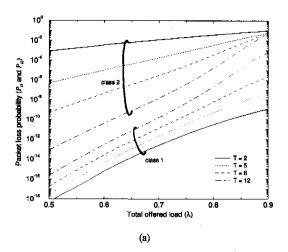

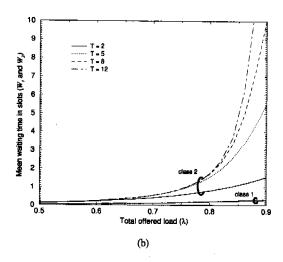

While the speed-up factor and the buffer size affect largely the overall average performance, the threshold T and the scheduling parameter p have an effect on the performance differences between the two classes. Fig. 4(a) shows that by varying the threshold T we can control loss probability differences very dynamically. The smaller the threshold is, the larger the loss probability are. The threshold also has differences non-negligible effect on the mean waiting time performances as shown in Fig. 4(b). Whereas the mean waiting time of class 1 packets remains nearly unchanged as the threshold increases, that of class 2 packets gets larger at higher loads. This is due to more class 2 packets entering and waiting in the input queue instead of being rejected. However, eventually the mean waitin time curves of class 2 packets are bounded by that of the input queue with the scheduling scheme only (i.e., with T=K-1).

Fig. 4 Changes of performance differences between two classes with varying threshold T(=2,5,8,12) for C=2, K=15, HOL scheme, and r=0.5. (a) Packet loss probabilities vs. total offered load λ. (b) Mean waiting times vs. total offered load λ.

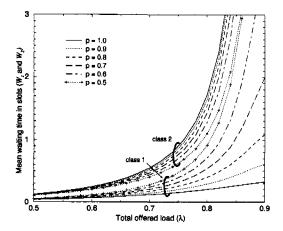

In Fig. 5, we show that by varying the scheduling parameter p we can also control the waiting time performance differences flexibly. We have larger differences as we increase p. As

expected, we observed that the scheduling parameter has an negligible effect on the loss performance, except only slight increases in loss probabilities with increasing p.

Fig. 5. Changes of performance differences between two classes with varying scheduling parameter p(=1.0,..., 0.5) for C=2, K=15, T=10 and r=0.5. Mean waiting times vs. total offered load  $\lambda$ .

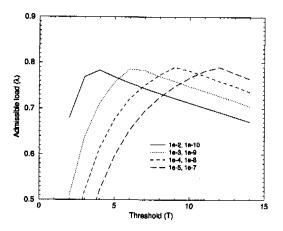

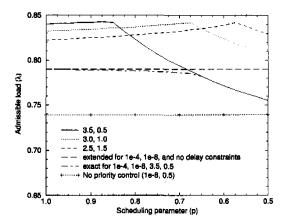

In the next set of figures, we examine the admissible load. Since it is clear that the switch can admit more loads by increasing the speed-up factor or the buffer size, we here focus on the admissible load change according to the threshold and the scheduling parameter. From the performance controllability with the threshold T and the scheduling parameter p, as shown in Figs. 4(a) and 5, we can guess that the admissible load can be maximized by adjusting T and p according to the loss and delay QoS of the two class traffic. With the next two graphs, we illustrate how we can achieve the maximum admissible load for a wide range of QoS gaps between the two classes.

First, in Fig. 6, we show the admissible load versus the threshlod with varying loss constraints: four curves for four different loss QoS sets assuming no delay QoS. We verify that the wider the loss QoS differences are, the system with the wider loss performance differences (i.e., the smaller threshold) accept more traffic. Note that this graph is drawn for HOL, i.e., p=1.0. However, since loss curves changes only slightly as the scheduling parameter p changes, as seen in

the Fig. 5, these four curves will remain nearly unchanged even if the scheduling parameter changes. This means that the optimal threshold value which makes the admissible load maximum for p=1.0 can be safely regarded also as the optimal one for any p between 1.0 and 0.5. For example, for any value of the scheduling parameter p in the range, the threshold T=9 can be considered as optimal for class 1 and 2 loss constraints of  $10^{-8}$  and  $10^{-4}$  respectively.

Fig. 6. Admissible load ( $\lambda$ ) vs. threshold (T) with warying loss constraints but no delay constraints for C=2, K=15, HOL(p=1.0) and r=0.5.

Once we have chosen the optimal threshold, we can then select an appropriate value of the scheduling parameter p. This can be shown by using Fig. 7. The figure shows the admissible load versus the scheduling parameter with varying delay constraints. Here, we again verify that the wider the delay QoS differences are, the system with the wider delay performance differences (i.e., the larger scheduling parameter) admit more traffic. For the case of both loss and delay constraints imposed together, to identify the range of p within which the maximum load exists, we simply extend the value of the admissible load obtained with the optimal T, in Fig. 7. For example, for 10<sup>-4</sup> and 10<sup>-8</sup> of the loss QoSs as well as 3.5 and 0.5 for the mean waiting time QoSs, we achieve the admissible load of about 0.79 with T=9 from Fig. 6 and then we extend this value of the admissible load in Fig. 7 (See the long dashed line in the figure), to get an appropriate range of p, i.e.,  $0.7 \le p \le 1.0$ . The results are verified by an exact curve drawn for both QoSs imposed together. Also, the results are compared from the admissible load curve obtained with no priority control where most stringent QoS constraints should be imposed.

Fig. 7. Admissible load  $(\lambda)$  vs. scheduling parameter (p) with varying delay constraints but no loss constraints for C=2, K=15, T=9 and r=0.5.

#### V. Conclusion

In this paper, we analyzed input queueing ATM switches with the partial buffer sharing and the general state-dependent scheduling schemes. The analysis was done in two steps. In the first step, we considered a tagged virtual HOL queue and computed the HOL contention times of two classes of traffic. In the second step, we separated an input queue from the switch and analyzed the combined priority schemes to get loss probabilities and mean waiting times of the two classes.

From the numerical results obtained after the recursive computation, we showed the performance behavior with various system parameters. We showed that while the speed-up factor and the buffer size affect the overall average performances, the threshold T and the scheduling parameter p affect dynamically the performance differences between the two classes. We also showed that for a wide range of QoS gaps

between two classes, we can maximize the admissible load, by first adjusting T against the loss QoS and then p against the delay QoS.

#### References

- [1] ITU-T, Recommendation I.121, "Broadband Aspects of ISDN," 1991.

- [2] D. E. McDysan and D.L. Spohn, ATM Theory and Application. MCGraw-Hill, 1995.

- [3] J. J. Bae and T. Suda, "Survey of Traffic Control Schemes and Protocols in ATM Networks," *Proceedings of the IEEE*, vol. 79, no. 2, pp. 170-189, Feb. 1991.

- [4] H. Kröner, "Comparative Performance Study of Space Priority Study of Space Priority Mechanism for ATM Networks," in *Proc. IEEE INFOCOM'90*, pp. 1136-1143, 1990.

- [5] J. W. Roberts and A. Gravey, "Recent Results on B-ISDN/ATM Traffic Modelling and Performance Analysis-A review of ITC 13 Papers," in Proc. IEEE GLOBECO'91, pp. 1325-1330, 1991.

- [6] X. Cheng and I. F. Akyildiz, "Analysis of a Finite Buffer Queue with Different Scheduling and Push-Out Schemes,"

Performance Evaluation, vol. 19, no. 4, pp. 317-340, Apr. 1994.,

- [7] J.S.-C. Chen and R. Guérin, "Performance Study of an Input Queueing Packet Switch with Two Priority Classes," *IEEE Trans. Commun.*, vol 39, no. 1, pp. 117-126, 1991.

- [8] A.K. Gupta and N. D. Georganas, "Priority Performance of ATM Packet Switches," in *Proc. IEEE INFOCOM'92*, pp. 5D.2.1-5D.2.7, 1992.

- [9] S.-Q. Li, "Nonuniform Traffic Analysis on a Nonblocking Space-Division Packet Switch," *IEEE Trans. Commun.*, vol. 38, no. 7, pp. 1085-1096, Jul. 1990.

- [10] M. J. Karol, M. G. Hluchyj, and S. P. Morgan, "Input Versus Output Queueing

- on a Space-Division Packet Switch," *IEEE Trans. Commun.*, vol. COM-35, no. 12, pp. 1347-1356, Dec. 1987.

- [11] H. Takagi, Queueing Analysis: A foundation of Performance Evaluation, Volume 3: Discrete-Time Systems. Tokyo: North-Holland, 1993.

- [12] H. Takagi, Queueing Analysis: A foundation of Performance Evaluation, Volume 1: Vacation and Priority Systems, Part 1. Tokyo: North-Holland, 1991.

- [13] O. J. Boxma and W. P. Groenendijk,

"Waiting Times in Discrete-Time

Cyclic-Service System," IEEE Trans.

Commun., vol. 36, no. 2, pp. 164-170,

Feb. 1988.

이 계 상(Kye-Sang Lee)

정회원

1979년 2월:서울대학교 공과 대학 자원공학과 학사

1981년 2월:서울대학교 대학 원 전자공학과 석 사

1997년 2월 : 한국과학기술원 전기및전자공학과 박사

1981년 10월~1982년 2월: 한국전자통신연구원 위 촉연구원

1982년 3월~1997년 8월 : 한국전자통신연구원 선임 연구원 (과제책임자, 실 장)

1997년 9월~현재 : 동의대학교 전자통신공학과 전 임강사

1997년 9월~1998년 12월 : 한국전자통신연구원 초 빙연구원

<연구분야 인터넷 Internetworking, 광대역 통신망, 네트워크 QoS, 정보통신 표준화