# 시스템 효율향상을 위한 이동통신망 Rake Finger 시스템 설계에 관한 연구

정회원 이 선 근\*, 임 순 자\*\*

## A Study on the Rake Finger System Design for the System Performance Improvement in the Mobile Communications

Seon-Keun Lee\*, Soon-Ja Lim\*\* Regular Members

요의

이동통신 무선접속 기술 요소 중 하나인 MC-CDMA 시스템의 레이크 수신기는 다수 채널로 전송된 신호들을 동시에 복조해야 하므로 트래픽 채널을 복조하는 데이터 상관기의 수가 왈쉬 코드 채널의 수만큼 증가하게 되어 신호처리의 복잡도가 증가되는 단점을 갖게 된다. 본 논문에서는 데이터 상관기들의 증가로 인한 데이터 처리시간 지연을 감소시키기 위해 Walsh Switching, 공유 accumulator, pipeline-FWHT 알고 리즘을 적용한 새로운 레이크 수신기 구조를 제안했다. 모의실험 결과, 왈쉬 코드 채널의 수 N=4에 대한 데이터 상관기의 연산 동작 수는 512 가산에서 160 가산으로 약 3.2배 감소하였고, 데이터 처리시간은 18.3% 감소하였음을 확인하였다.

Key Words: MC-CDMA; Rake Finger; VHDL; ASIC

#### **ABSTRACT**

In this paper, we proposed the new structure of the Rake Finger using Walsh Switch, the shared accumulator, and the pipeline-FWHT algorithm for reducing the signal processing complexity resulting from the increase of the number of data correlator. The function simulation of the proposed architecture is performed by Synopsys tool and the timing simulation is performed by Compass tool. The number of computational operation in the proposed data correlators is 160 additions and the conventional ones is 512 additions when the number of walsh code N=4. As a result, it is reduced about 3.2 times other than the number of computational operation of the conventional ones. Also, the result shows that the data processing time of the proposed Rake Finger architecture is 90,496[ns] and the conventional ones is 110,696[ns]. It is 18.3% faster than the data processing time of the conventional Rake Finger architecture.

논문번호: 030311-0722, 접수일자: 2003년 7월 22일

<sup>\*</sup> 원광대학교 전자공학과 (caiserrisk@korea.com)

<sup>\*\*</sup> 원광대학교 전자공학과 BK21 산학계약교수

#### I. 서 론

IMT-2000은 ITU-R등에서 표준을 제정하고 있는 제 3세대 이동통신 시스템으로써 음성, 데이터, 영상 혹은 비디오 등의 다양한 서비스 제공을 요구하고 있다<sup>[11][2][3]</sup>.

IMT-2000의 무선접속 기술 요소 중 영상 혹은 비 디오 등의 다량의 정보를 고속으로 전송하기 위한 multirate 전송방법은 VSG(Variable Spreading Gain)-CDMA 시스템과 Multi-Code(MC) CDMA 시 스템, 그리고 Multi-Carrier CDMA 시스템 등으로 나눠진다. VSG-CDMA 방식은 높은 전송률에서 확 산이득 감소 현상이 나타나지만 Multi- Code CDMA 방식은 높은 전송률에서 확산이득 감소 현상 이 나타나지 않으며 전송 속도를 상황에 따라 유연 하게 조절할 수 있는 장점이 있다. 따라서 한정된 대역폭 안에서 사용자가 요구하는 여러가지 전송 속 도와 서비스를 제공할 수 있다. Multi-Carrier CDMA 방식은 사용자에게 한개 이상의 주파수를 할 당하여 전송 데이터를 병렬로 변환 후 전송하는 방 식이다. 그러나 다중경로는 두 가지 셀이 중첩된 상 황에서 Multi-Carrier 방식의 성능이득을 감소시킨다. 다중경로채널에서 지연확산 효과를 줄일 수 있는 방 법으로는 방향성 안테나와 등화기(equalizer)를 사용 하면 되지만 높은 데이터 전송률에서는 매우 복잡한 등화기가 필요하게 된다. 이러한 Multi-Carrier 방식 과는 달리 Multi-Code 방식은 하나의 주파수 대역을 사용하여 서로 직교 열로 각각의 데이터를 확산해 줌으로써 데이터간 간섭을 최소화시킨다. 또한 고속 데이터 전송을 요구하는 사용자에 대해 하나 이상의 왈쉬채널을 할당함으로써 IMT-2000에서 요구되는 주 파수 사용 효율을 만족시키는 기술이다[415]. 일반적으 로 MC-CDMA 시스템은 DS-CDMA 시스템에서와 같이 다중경로 채널의 주파수 선택적 감쇄의 영향을 상쇄시키기 위해 Rake 수신기를 사용한다. 만약 기 지국이 사용자로부터 높은 데이터 서비스를 요구받 을 경우, 기지국은 데이터를 다수의 트래픽 채널로 나누어 사용자에게 전송하게 되며 사용자는 늘어나 는 트래픽 채널의 개수만큼 데이터 서비스를 받을 수 있게된다. 이러한 데이터 서비스를 제공받기 위해 서 이동국의 Rake 수신기는 다수의 채널로 나누어 전송된 신호들을 동시에 복조할 수 있는 구조로 되 어 있어야 한다. MC-CDMA 시스템의 이동국 Rake 수신기는 다수의 트래픽 채널을 동시에 복조해야 하

므로 레이크 수신기에서 채널을 복조하는 데이터 상 관기들의 수가 왈쉬코드 채널의 수만큼 증가하게 된 다. 이로 인해 이동국에서 중요한 고려 사항인 신호 처리의 복잡도가 증가하여 데이터 처리시간과 전력 소비가 증가하게 된다.

따라서 본 논문에서는 데이터 상관기들의 증가로 인한 신호처리의 복잡도를 줄여 전체 레이크 수신기 의 데이터 처리 시간을 감소시키기 위해 Walsh Switch와 공유 accumulator, 파이프라인 FWHT(Fast Walsh Hadamard Transform) 알고리즘을<sup>61</sup> 적용한 새로우 레이크 수신기 구조를 제안했다.

#### Ⅱ. 기존 레이크 수신기 시스템 구조

MC-CDMA 시스템은 DS-CDMA 시스템에서와 같 이 다중경로 환경에서 신호들을 수신하는데 최적의 기술인 Rake 수신기를 사용하여 다줏경로 채널의 주 파수 선택적 감쇄의 영향을 상쇄한다<sup>[3][6]</sup>. 이동통신은 다중경로 페이딩 채널이므로 각 경로의 데이터를 복 조하기 위해서는 모든 경로의 신호를 이용하는 것이 최상이나 3개 이상의 다중경로 신호를 결합하더라도 성능의 큰 향상이 없기 때문에 일반적으로 순방향 링크의 경우 3개의 레이크 수신기를 사용한다. IMT-2000 다중경로 환경의 경우 6개의 경로 신호가 있으나 수신단의 레이크 수신기는 3개이므로, 수신기 는 6개의 경로 신호중에서 평균전력이 가장 큰 3개 의 경로 신호만을 가지고 복조하게 된다. MC-CDMA 수신기는 서로 다른 데이터 경로들에 대 해 데이터의 역확산과 복조를 위해 사용하는 레이크 수신기 블록의 수정만을 통해 Rake 수신기를 그대로 이용할 수 있다.

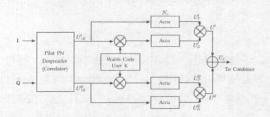

각 레이크 수신기 블록은 다수의 왈쉬코드 채널들을 추적하고 획득하기 위한 타이밍 정보를 제공하는 공통된 하나의 타이밍 블럭을 포함하고 있다. 그리고 이러한 데이터 채널들을 복조하기 위한 다수의 데이터 상관기와 왈쉬함수 발생기들을 필요로 한다. I, Q 채널을 모두 고려한 단일 채널일 때의 기존 데이터 상관기 구조는 그림 1과 같다.

Pilot PN despreader(Correlator)를 통해 출력된 파일럿 I, Q 신호 샘플들은 각각 심볼 주기(N<sub>c</sub>) 만큼 어큐뮬레이터에서 누적됨으로써 파일럿 신호를 복원한다. 데이터를 복원하기 위해 왈쉬함수 발생기로부터 출력된 왈쉬 시퀀스는 각각 파일럿 I와 Q

신호 샘플들과 상관되고 이 신호들은 각각의 어큐뮬 레이터에서 심볼 주기(N<sub>c</sub>) 만큼 누적된다.

그림 1. 단일 채널의 기존 데이터 상관기

그리고 위상 기준신호인 파일럿 I 및 Q 신호와 채널 weighting을 한 후 컴바이너를 통해 각 레이크 수신기의 출력 심볼들은 합쳐지게 된다. Pilot PN despreader를 거친 사용자 K에 대한 I, Q 신호는 식 (1)로 정의할 수 있다. 이때 사용자의 채널 크기(channel amplitude)는 1로 가정한다.

$$U_{1K}^{I} = 2(x_{I}W_{K} + A)\cos\phi + \delta_{K}^{I}$$

$$U_{1K}^{Q} = 2(x_{I}W_{K} + A)\sin\phi + \delta_{K}^{Q}$$

(1)

여기서,  $x_i$ 은 비트 속도  $R_b$ 에서의 사용자데이터이고,  $W_K$ 는 사용자 K에 대한 왈쉬 코드다. A는 파일럿 이득을 나타내며,  $\phi$ 는 수신된 신호의 위상 천이(phase shift)  $e^{i\phi}$ 를 나타낸다. 칩 수( $N_c$ ) 만큼 누적된 후 복원된 파일럿 위상 신호 I, Q는 식(2)와 같다.

$$\begin{split} U^{I}_{P} &= \sum_{K=0}^{N_{c}-1} (2(x_{i}W_{K} + A)\cos\phi + \delta^{I}_{K}) \approx 2N_{c}A\cos\phi \\ U^{Q}_{P} &= \sum_{K=0}^{N_{c}-1} (2(x_{i}W_{K} + A)\sin\phi + \delta^{Q}_{K}) \approx 2N_{c}A\sin\phi \end{split} \tag{2}$$

왈쉬 역확산과 심볼 주기만큼 누적된 데이터 신호는 식 (3)과 같이 나타낼 수 있다.

$$U_{D}^{I} = \sum_{K=0}^{N_{c}-1} W_{K} U_{1K}^{I} \approx 2 N_{c} x_{I} \cos \phi$$

$$U_{D}^{Q} = \sum_{K=0}^{N_{c}-1} W_{K} U_{1K}^{Q} \approx 2 N_{c} x_{I} \sin \phi$$

(3)

심볼 속도에서 채널 weighting된 신호는 식 (4)와 같다.

$$U^{I} = U^{I}_{P} \cdot U^{I}_{D} = 4N^{2}_{c}Ax_{I}\cos^{2}\phi$$

$$U^{Q} = U^{Q}_{P} \cdot U^{Q}_{D} = 4N^{2}_{c}Ax_{I}\sin^{2}\phi$$

(4)

마지막 단계의 I, Q 덧셈(Adder) 부분의 데이터 출력 신호는 식 (5)와 같다.

$$U_C = U^I + U^Q = 4N^2_c A x_1 (5)$$

### Ⅲ. 시스템 효율향상을 위한 제안된 레이크 수신기 구조

제안된 레이크 수신기는 Walsh Switch, 공유 accumulator 그리고 파이프라인 FWHT를 이용하여 데이터 상관기의 연산동작 수를 감소시켜 전체 레이크 수신기의 데이터 처리 지연시간을 감소시켰다. 공유 accumulator 방법은 심볼 속도에서 동작하는 N개의 어큐뮬레이터 대신 심볼 속도의 N배에서 동작하는 하나의 어큐뮬레이터를 이용한 time-multiplexing에 의해 이루어진다.

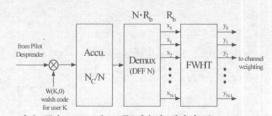

이것은 ADC(Analog-to-Digital Convertor)에 사용되는 고주파 클럭 신호가 공유된 accumulator의 time-multiplexing 동작에 이용될 수 있다는 점에 의한 것이다. 공유 accumulator를 이용한 제안된 구조는 그림 2와 같다.

그림 2. 공유 accumulator를 이용한 제안된 구조

적절하게 선택된 길이  $N_c$ 의 기본 왈쉬 코드는  $N_c/N$  길이와 같은 N개의 segments로 나누게 되는데, 이는 심볼 속도의 N배에서 동작하는 어큐뮬레이터를 이용함으로써  $N_c/N$  길이와 같은 왈쉬 코드 채널 N개를 얻을 수 있다. 여기서 N은 2의 배수이고  $N_c$ 와 같거나 작다. 따라서  $N_c/N$  길이의 sub-walsh 코드 N개를 얻게 된다. 사용자 K에 대해 다중코드 신호를 부호화하기 위하여

사용하는 왈쉬 코드들 간에 요구되는 관계는 식 (6)과 같다.

$$W(K, i) = W_{K+i(N_c/N)}$$

(6)

여기서, 사용자 수  $K=0\cdots N_c/N-1$  이고 왈쉬 코드 채널 인텍스  $i=0\cdots N-1$  이다. 식 (6) 의 관계에 의해 각 코드 W(K,i)는 차수 N의 왈쉬 코드에 따라 배열된 길이  $N_c/N$ 의 N개 sub-walsh 코드들로 구성된다. N=4에 대한 사용자 K의 왈쉬 코드 W(K,i)는 식 (6)에 의해 식 (7)과 같은 코드열을 가지게 된다. 여기서 심볼 A는 순차적인 상관이 수행되는 길이  $N_c/N$ 의 sub-walsh 코드를 나타낸다. 집합 W(K,i)에서 모든 왈쉬 코드들은 차수 N=4의 overlay된 왈쉬 코드에 따라 각각 sub-walsh 코드 A와 A의 modulo-two inverse 인 A를 만든다.

$$W(K,0) = [AAAA]$$

$$W(K,1) = [A\overline{A}A\overline{A}]$$

$$W(K,2) = [AA\overline{A}\overline{A}]$$

$$W(K,3) = [A\overline{A}\overline{A}A]$$

(7)

식 (7)의 조건을 만족하는 왈쉬 코드 열을 선택하여 변조된 신호를 s(t)라 할 때 송신된 신호는 식 (8)과 같다.

$$s(t) = M(t) \cdot [C_{I}(t) \cos \omega_{C} t + C_{Q}(t) \sin \omega_{C} t]$$

$$M(t) = \sqrt{P_{C}} \{b_{0}(t) W(K, 0) + b_{1}(t) W(K, 1) + b_{2}(t) W(K, 2) + b_{3}(t) W(K, 3)\}$$

$$= \sqrt{P_{C}} W(K, i) [X_{0} X_{1} X_{2} X_{3}]$$

(8)

수신 신호의 복원시 PN 칩 동기 및 주파수 동기 가 맞았다고 가정하면 수신 신호의 역확산된 신호는 식 (9)와 같이 표현할 수 있다.

$$r(t) = \sum_{i=0}^{N-1} \{ \beta \sqrt{P_C} b_i(t) W(K, i) \cos \phi \} + n(t)$$

(9)

N=4인 경우에 대해 식 (9)는 식 (10)으로 정의할

수 있다.

$$r(t) = \beta \sqrt{P_C} W(K, i) \cos \phi \left[ X_0 X_1 X_2 X_3 \right] + n(t)$$

(10)

식 (10)에서 적절하게 선택된 데이터에 대해  $N_c/N$ 마다 reset되는 공유 accumulator를 거친 N=4에 대한 중간 상관값들은 차수 N의 FWHT 블록을 통해 서로 다르게 더하고 빼는 과정을 수행하여 N개의 완전한 데이터 상관기 출력들을 얻을수 있는 신호를 발생하게 된다. 결국, N=4인 경우의 데이터는 식 (11)과 같이 구할 수 있다.

$$b_{0} = W(K, \hbar) [ r(t)^{X_{0}} + r(t)^{X_{1}} + r(t)^{X_{2}} + r(t)^{X_{3}} ]$$

$$b_{1} = W(K, \hbar) [ r(t)^{X_{0}} - r(t)^{X_{1}} + r(t)^{X_{2}} - r(t)^{X_{3}} ]$$

$$b_{2} = W(K, \hbar) [ r(t)^{X_{0}} + r(t)^{X_{1}} - r(t)^{X_{2}} - r(t)^{X_{3}} ]$$

$$b_{3} = W(K, \hbar) [ r(t)^{X_{0}} - r(t)^{X_{1}} - r(t)^{X_{2}} + r(t)^{X_{3}} ]$$

(11)

여기서  $n(t)^{X_0}$ ,  $n(t)^{X_1}$ ,  $n(t)^{X_2}$ ,  $n(t)^{X_3}$ 은 각각 n(t)의  $X_0$ ,  $X_1$ ,  $X_2$ ,  $X_3$  신호열 성분을 나타낸다. 그러므로, 하나의 어큐뮬레이터와 왈쉬 코드 채널만으로 기존 N채널 데이터 상관기와 같은 기능을 하게 된다. Walsh Switch는 어큐뮬레이터에 원하는데이터 채널과 파일럿 채널을 스위치 하기 위한 것이며 왈쉬 코드의 상태에 따라 스위치 되는 binary switch이다. 또한 Walsh Switch는 파일럿과 데이터어큐뮬레이터의 결과를 공유할 수 있도록 하기 위한 것이다.

변조되지 않은 신호인 파일럿 신호는 논리 레벨 all-zero 왈쉬 코드를 사용하고 데이터를 위한 왈쉬 코드는 논리레벨 1, 0으로 이루어져 있으므로 왈쉬 코드 값들을 1과 0의 성분으로 분리하기 위해, 왈쉬 코드 값이 논리레벨 0이면 왈쉬 함수 항  $W_K$ 는 +1이 되고 스위치는 +1을 스위치 한다. 왈쉬 코드 값이 논리레벨 1이면  $W_K$ 는 -1이 되고 스위치는 -1을 스위치 하게된다.

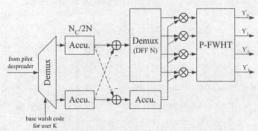

제안된 N채널 데이터 상관기는 I, Q 채널에 대해 각각 공유 accumulator에서  $N_c$ 의 연산 동작을 수행하고 cross adder 부분과 파일럿 어큐뮬레이터에서 3N, 파이프라인 FWHT 블록에서  $N/2 \times \log_2 N$ 의 연산 동작을 요구하게 된다. 즉, 기존의 N채널 데이터 상관기는 I, Q 채널에 대해  $2(N_c \times N)$ 의 연

산 동작 수를 요구하게 되지만 제안된 구조는  $2\{N_c+3N+(N/2\times\log_2N)\}$ 의 연산 동작만을 수행하면 된다. 제안된 N채널 데이터 상관기를 포함한 전체 레이크 수신기의 구조는 그림 3과 같다. 타이밍 복원 블록(Pilot early/late Correlator)과 입력 신호와의 주파수 차이를 찾아내어 에러를 보정할 수 있는 신호를 생성하는 블록은 채널 수 증가에 관계없이 공통된 하나의 블록으로 처리되므로 기존의 구조와 같다.

그림 3. 제안된 레이크 수신기 전체 구조

#### IV. 모의실험 및 고찰

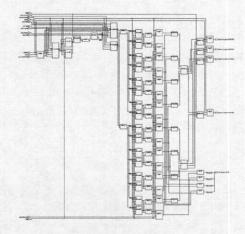

모의실험은 VHDL을 이용하여 설계한 레이크 수 신기의 전체 회로에 대해 Synopsys Ver. 1999. 10, KG-75 library를 사용하여 회로합성 및 function simulation을 수행하여 레이크 수신기의 기능에 대한 동작 특성을 모의실험하였다. 제안된 레이크 수신기 의 합성 회로는 그림 4과 같다. 기존 레이크 수신기 에서는 수신된 디지털 신호 serial[3:0]을 입력신호로 사용하였고, 4개의 왈쉬 함수 발생기의 6비트 인덱스 값들은 각각 OFH, 1FH, 2FH, 3FH를 사용하였다. Timing tracking에 의해 발생된 pn\_en 신호가 '1'일 때 PN 코드 발생기는 파일럿 on time 신호가 발생 하게 되고, Correlator의 인에이블 신호인 corr\_enb가 '1'일 때, 매 칩 시간마다 디지털 수신신호의 병렬 4 비트를 입력신호로 제공받아 replica PN 코드와의 매칭 여부를 판별하여 매칭도에 따른 코드 값을 발 생시켰다.

왈쉬 함수 발생기의 walsh\_load 신호가 '1'일 때 왈쉬 함수 발생기내의 레지스터는 동작하게 되고 64칩이 지나면 왈쉬 함수 발생기를 reset 시키게 된다. Correlator의 출력신호인 z\_1, z\_0는 왈쉬 함수 발생기의 출력신호인 walsh\_chip과 디커버링 동작을 수행한 후 어큐뮬레이터에서 각각 64칩 동안 누적된

후 출력된다. 이 출력신호는 출력된 파일럿 신호와 채널 weighting을 수행하게 된다.

그림 4. 레이크 수신기 전체 회로

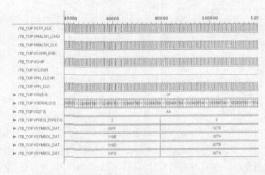

제안된 구조는 1개의 왈쉬 함수 발생기를 사용하는데, Base Walsh index로 OFH를 사용하였다. 단위 정합필터 회로의 입력값 ss[3:0]에 대한 칩 신호를 발생시키기 위하여 링 카운터의 제어신호 "10101010"에 대한 Correlator의 출력 값인 z\_i, 함수 발생기의 출력 walsh\_chip이 논리 '0'일 때 각각 add<sup>1</sup>, add<sup>Q</sup> 신호를 출력하는 어큐뮬레이터로 스위치 되고, 논리 '1'일 때는 subst', subst<sup>Q</sup> 신호를 출력하는 어큐뮬레이터로 스위치 된다. 각각의 어큐뮬레이터는 8칩 동안 누적되고 한 심볼 동안 4번 reset된다. add st 어큐뮬레이터의 출력신호인 subst1, add<sup>Q</sup>와 subst<sup>Q</sup>는 뎃셈 연산과 뺄셈 연산을 수행한다. 뺄셈 연산을 수행한 결과는 다시 한 번 어큐뮬레이터에서 4칩 동안 누적되어 파일럿 신호를 복원하고, 뺄셈 연산을 수행한 결과는 레지스터에 순차적으로 저장되었다가 파일럿 신호가 출력되는 순간에 채널 weighting을 수행한다. 이 weighting 값들은 파이프라인 FWHT에서 서로 다르게 더하고 빼는 과정을 통해, 그림 5에 나타난 것처럼 레이크 수신기의 출력신호인 Symbol\_data0, Symbol\_data1, Symbol\_data2, Symbol\_data3들이 각각 수신신호 성분을 포함한 13비트씩, 기존 구조에 비해 25칩 먼저 출력됨을 확인할 수 있었다.

제안된 레이크 수신기의 동작 특성에 대해,

9.8304[MHz]의 시스템 클럭과 1.2288[MHz]의 침 클럭을 사용하여 Compass tool로 모든 게이트 지연과 routing 지연을 포함한 timing simulation을 수행하였다. 제안된 구조는 데이터 상관기 부분의 연산 동작 수를 약 3.2배 정도 줄일 수 있었고 데이터 처리 시간은 110,696[ns]에서 90,496[ns]로 18.3% 줄일 수 있었다. 결론적으로 신호 처리의 복잡도를 개선시켜 데이터 처리 시간을 감소시키는 제안된 구조는 좀 더 높은 고속의 데이터 서비스를 제공받기 위한 이동국 수신단에 있어서 채널의 수가 증가될수록 더욱 효율적인 것으로 나타났다.

그림 5. 제안된 레이크 수신기의 모의실험결과

#### V. 결 론

본 논문에서는 데이터 상관기들의 증가로 인한 데 이터 처리시간 지연을 감소시키기 위해 Walsh Switch, 공유 accumulator, 그리고 파이프라인 FWHT 알고리즘을 적용한 새로운 레이크 수신기 구 조를 제안했다. 제안된 레이크 수신기의 N채널 데 이터 상관기는 2{N<sub>c</sub>+3N+(N/2×log<sub>2</sub>N)}의 연산 동작만을 수행함으로써 기존의 데이터 상관기에 비 해 연산 동작의 수가 약 3.2배 감소하였다. 그리고 설계된 전체 레이크 수신기에 대한 function simulation 결과 25칩 먼저 출력되었고 timing simulation을 수행한 결과, 데이터 처리시간이 110,696[ns]에서 90,496[ns]로 18.3%가 감소되었다. 따 라서 제안된 레이크 수신기 구조는 CDMA 방식 및 Multi-Code 방식의 통신 시스템에 적용이 가능하며, IMT-2000 시스템에서 다양한 data rate을 가진 고속 의 멀티미디어 서비스를 제공하는데 있어서 채널의 수가 증가될수록 더욱 효과적일 것으로 사료된다.

#### 참고문헌

- [1] E. K. Wesel, "Wireless Multimedia Communications", Addison Weselv, 1998.

- [2] T. Ojanperä, R. Prasad, "Wideband CDMA for Third Generation Mobile Communications", Boston London: Artech, 1999.

- [3] 기술정보센터 정보조사분석팀, "차세대 이동통신 시스템", 한국전자통신연구원, 1999.

- [4] Tero Ojanperä, Ramjee Prasad, "An Overview of Air Interface Multiple Access for IMT-2000/ UMTS", IEEE Comm. Magazine, vol. 36, no. 9, pp. 82-86, September 1998.

- [5] P. Kuganesan and K. B. Letaief, "High-Speed Data Transmission with Multicode Modulation and Turbo-codes for Wireless Personal Communications", IEEE ICC., pp. 959-963, June 1997.

- [6] N. Ahmed, K. R. Rao, "Orthogonal Transform for Digital Signal Processing", 1975.

이 선 근(Seon-Keun Lee) 정회원 Journal of Electrical Engineering Information Science Vol. 4, No. 6, Dec. 1999

임 순 자(Soon-Ja Lim)

1985년 2월 : 원광대학교

전자공학과 졸업

1991년 8월 : 원광대학교

전자공학과 석사

2001년 8월 : 원광대학교

전자공학과 박사 2003년 8월-현재 : 원광대학교

BK21 산학 계약교수

<주관심분야> 멀티미디어 통신, 영상정보처리 및 압축