# 무선 멀티미디어 통신망의 성능 향상을 위한 OFDM FFT 설계에 관한 연구

정회원 강정용\*, 이선근\*\*

# A Study on OFDM FFT Design for Performance of Wireless Multimedia Network

Jung-yong Kang\*, Seon-keun Lee\*\* Regular Members

요 약

이동 멀티미디어 서비스를 위한 통신 시스템에서 고속으로 데이터를 송신하고 수신함에 따라 발생하는 인접 심 벌간의 간섭(Inter Symbol Interference · ISI) 왜곡을 줄이기 위한 방식으로 직교 주파수 분할 다중화(Orthogonal Frequency Division Multiplexing : OFDM) 방식에 대한 연구가 활발하게 진행되고 있다

고속 무선 LAN이 표준방식으로 채택한 OFDM 방식이 부 반송파의 수가 많아짐에 따라 변복조부를 실제 시스템으로 구현하기가 어려운 단점이 있었다. 그러므로 본 논문에서는 파이프라인 방식을 이용해서 변복조부를 설계하여 많은 수의 버터플라이(Butterfly) 연산자를 감소시켰다 또한 고속의 처리속도를 만족시키기 위해서 64 포인트를 처리하는 버터플라이 구조를 각각 32 포인트씩 병렬처리 하도록 구성하였다.

Key Words: Wireless, OFDM, FFT, Design

#### **ABSTRACT**

The efficient hardware design of the FFT algorithm is important in wide variety of DSP One example is OFDM(Orthogonal Frequency Division Multiplexing) based WLAN(Wireless Local Area Network) systems which place high requirements on throughput and power consumption on FFT.

The output RAM is composed of two banks of 64×W The banks are swapped immediately following the falling edge of the start signal strobe. This bank swapping allows 64-point FFT to continue processing samples and to continue filling the alternative bank, without affecting the data flow outputs.

#### I . 서 론

증가하는 광대역 무선 서비스의 수요에 부응하고 각각의 기업체에서 생산된 제품들 사이의 호환성을 만족시키기 위하여 제정된 표준안은 크게 IEEE 802.11, ETSI(European Telecommunication Standard Institute) BRAN (Broadband Radio Access Networks) 프로젝트의 HIPERLAN(High Performance Radio LAN) 규격, 미국 WIN(Wireless Information Networks) 포럼의 SUPERNET(Shared Unlicensed Personal Radio Network), 일본 MMAC-PC(Multimedia Mobile Access Communication Systems-Promotion Council) 규격, ATM 포럼의 WATM(Wireless ATM)-WG 규격으로 분류할 수 있다[1]

그림 1의 IEEE 802.11a에서는 5 GHz 대역을 사용하는 OFDM 방식의 고속 무선 LAN의 물리계층 및 PLCP(Physical Layer Convergence Procedure)를

<sup>\*</sup> 원광대학교 전자공학과 회로및시스템 연구실,

<sup>\*\*</sup> 원광대학교 전자공학과 회로및시스템 연구실(caiserrisk@korea com), 논문번호 kics2004-06-066, 접수일자 2004년 6월 8일

규정하고 있다. 표 1은 OFDM PLCP 프리앰블, OFDM PLCP 헤더, PSDU(Physical Sublayer Service Data Units), tail 비트, pad 비트로 구성된 IEEE 802.11a의 데이터 전송을 위한 데이터 구조를 보여준다.[2]

그림 1 IEEE 802.11a 무선 모뎀 블록도

표 1 OFDM 물리계층의 파라미터

| Information<br>data rate | 6, 9, 12, 18, 24, 36, 48 and 54 Mbit/s<br>(6, 12 and 24 Mbit/s are mandatory) |  |  |

|--------------------------|-------------------------------------------------------------------------------|--|--|

| Modulation               | BPSK-OFDM, QPSK-OFDM<br>16-QAM-OFDM, 64-QAM-OFDM                              |  |  |

| Error correcting code    | K=7 (64 states) convolutional code                                            |  |  |

| Coding rate              | 1/2, 2/3, 3/4                                                                 |  |  |

| Number of subcarners     | 52                                                                            |  |  |

| OFDM symbol<br>duration  | 4 0 μs                                                                        |  |  |

| Guard interval           | 08 μs³(T <sub>GI</sub> )                                                      |  |  |

| Occupied<br>bandwidth    | 166 MHz                                                                       |  |  |

#### II. FFT 암고리즘 및 설계 방법

FFT 알고리즘은 크게 두 가지 회전인자의 곱셈이 있는 알고리즘과 회전인자의 곱셈이 없는 알고리즘으로 구분할 수 있다. 회전인자가 있는 알고리즘으로는 대표적으로 Cooley-Turkey 알고리즘과 DIT (Decimation In Time) 알고리즘, DIF(Decimation In Frequency) 알고리즘, split radix FFT 알고리즘 등이 있다[3]

DIT FFT 알고리즘은 N=2  $^{1}$ 인 DFT를 시간영역에서 짝수 항과 홀수 항으로 나누어서 분해한다. 먼저식 (1)의  $\chi(n)$ 을 짝수 항과 홀수 항으로 나누면 식과 같이 된다.

$$X(k) = \sum_{n=0}^{N-1} x(n) W_N^{kn}$$

$$= \sum_{n=0}^{N/2-1} x_{2n} W_N^{2kn} + \sum_{n=0}^{N/2-1} x_{2n+1} W_N^{(2n+1)k}$$

$$= \sum_{n=0}^{N/2-1} x_{2n} W_N^{2kn} + W_N^k \sum_{n=0}^{N/2-1} x_{2n+1} W_N^{2nk} \quad (1)$$

$$= \sum_{n=0}^{N/2-1} x_{2n} W_{N/2}^{2kn} + W_N^k \sum_{n=0}^{N/2-1} x_{2n+1} W_{N/2}^{2nk}$$

$$= X_{11}(k) + W_N^k X_{12}(k)$$

$$(k=0,1,\dots,7)$$

DIF FFT 알고리증은 Sande에 의해 제안되었으며 DIT FFT 알고리증의 변형이라 할 수 있다 DIT와 마찬가지로 N=2 V인 DFT인 경우 사용할 수 있으며  $-W^{2N}_{N}^{(n+N/2)}=W^{2N}_{N}^{\infty}$  특성을 이용하여 주파수 영역에서의 X(k)를 짝수 항과 홀수항의 주파수 표본으로 나누면 식 (2)와 (3)처럼 표현된다.

$$X(2r) = \sum_{n=0}^{N/2-1} (x(n) + x(n+N/2)) W_{N/2}^{rn}$$

(2)

$$X(2r+1) = \sum_{n=0}^{N/2-1} (x(n) - x(n+N/2)) W_N^r W_{N/2}^{rn} (3)$$

$$(r=0,1,\dots,N/2-1)$$

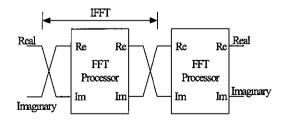

OFDM 시스템에서 OFDM의 변조는 IFFT, 복조는 FFT를 사용함으로써 그림 2와 같이 FFT 프로세서로 OFDM 변복조를 모두 구현할 수 있다.

그림 2 FFT 프로세서를 이용한 OFDM 모뎀

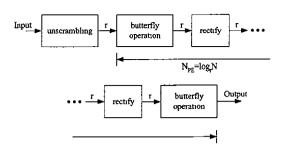

파이프라인 FFT 구조(Innear systolic array FFT)는 FFT 신호 호름도에서 각각의 열을 log ,A 개의 처리요소를 가지는 하나의 행으로 나누어 표현하며 가장 폭넓게 사용되는 FFT 구조로써 R2MDC, R2SDF, R4MDC, R4SDF, R4SDC 그리고 R22SDC 구조가 있다그림 3은 일반적인 파이프라인 FFT 구조를 나타내고 있다.

그림 3 파이프 라인 구조의 일반적인 형태

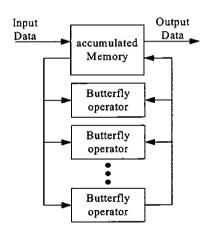

그림 4 SIC FFT 구조는 많은 신호처리 문제들을 해 결하는데 있어서 적용할 수 있는 SIC 구조를 기반으로 한다 일반적으로 SIC 구조는 공유 메모리를 사용하며 이 공유 메모리는 각각의 독특한 특성을 가지는 여러 개의 부분적인 메모리로 나뉘고 이 중에서 일부분은 일반적인 형태의 메모리 저장장소로써 이용이 된다[4]

그림 4 SIC FFT 구조의 일반적인 형태

SIC FFT 구조는 새로운 데이터가 FFT 프로세서에 입력되었을 때 그 데이터가 공유 메모리에 입력되고 버터플라이 연산자는 공유 메모리로부터 저장되어 있 는 입력 데이터를 얻게되며 버터플라이 연산에 의해 생성된 데이터를 공유 메모리에 저장한다 SIC FFT 구 조는 요구되는 처리율에 맞추어서 필요로 하는 연산자 의 수를 정확하게 사용할 수 있다. 요구되는 연산자의 수(N<sub>Rec</sub>)는 식 (4)와 같이 계산되어 진다

$$N_{BPE} = \left[ N_{BF} \frac{T_{BPE}}{T_{FFT}} \right] \tag{4}$$

식 (4)에서  $N_{PP}(=(Nr)\log_{r}N)$ 는 FFT 신호흐름

도에서 버터플라이의 수이고  $T_{\rm PMP}$ 는 버터폴라이 연산 자가 계산을 수행하기 위해 필요한 시간이며  $T_{\rm ext}$ 는 FFT를 계산하기 위해 필요한 시간을 나타낸다 SIC  $\operatorname{FFT}$  구조에서 요구하게 되는 메모리는 단지 N 개의 복소 워드만을 필요하며 이는 고정되거나 혼합된 형태 의 공통인수를 가지는 radix-r FFT 알고리즘은 In-place 특성을 가지고 계산되어지기 때문이다.

즉 데이터가 공유 메모리로부터 버터플라이 연산자 로 읽혀지게 되면 연산을 수행하는 메모리의 위치가 버터플라이 연산자로부터 계산된 결과를 저장하기 위 해서 다시 사용되어지게 된다.[5]

## Ⅲ. SIC 구조의 FFT 프로세서 설계 및 모의실험

적용된 Transform Algorithm은 규칙성과 대칭성이 뛰 어난 DIF FFT 알고리즘을 이용해서 설계하였다. 표 2 에서 볼 수 있는 것과 같이 서브캐리어 간격이 0.3125 MHz이고 처리 속도는 32 μs(=1/3125 KHz) 이내에서 처리되어야 한다. 64-point DIF FFT 프로세서를 설계하 기 위해 사용된 설계 규격으로는 수의 표현으로써는 고정 소수점(fixed point) 표현 방식을 이용하여 설계하 였으며 수의 형태는 하드웨어적으로 구현이 쉬운 부호 를 갖고 있는 2의 보수(2's complement) 표현을 사용하 였다.

표 2 FFT 프로세서 설계 규격

| DIF FFT 알고리즘 |  |

|--------------|--|

| 고정 소수점       |  |

| 부호를 갖는 2의 보수 |  |

| 54Mbps       |  |

| QPSK         |  |

| 52           |  |

| 48           |  |

| 4            |  |

| 0 3125MHz    |  |

| 12           |  |

| 20MHz        |  |

|              |  |

IEEE 802 11a 표준안에 적합한 FFT 프로세서를 설계 하기 위해서는 처리 속도가 32 us 안에서 처리되어야 하는데 일정한 규칙성을 가지고 있는 파이프라인 구조 는 많은 포인트의 FFT 프로세서를 설계하는 경우에는 전달 길이(transform length)에 따라서 단계 수가 증가하 고 이로 인한 단계 사이의 지연 때문에 처리속도가 감소하게 된다.

또한 대부분의 FFT 프로세서에서 대부분의 전력을 소모하는 부분이 버터플라이 연산자이기 때문에 많은 버터플라이의 연산자를 쓰는 경우 소비 전력이 증가하는 단점을 가지게 된다. 논문에서 적용하고자 하는 응용분야가 고속 무선 LAN이므로 노트북에 탑재시에 전력 소모가 적은 FFT 프로세서 필요하게 된다.

식 (5)는 본 연구에서 사용된 2의 보수 표기를 나타 내는 수식이다. 2의 보수 표기는 대부분의 컴퓨터에 서 사용되는데 이와 같은 표기 방법의 가장 큰 두 가 지 특징은 숫자 '0'을 정확히 표현할 수 있다는 것과 뺄셈의 구현이 쉽다는 것이다. 즉, 단지 피연산 (Operand) 함수의 보수를 더함으로써 구할 수 있다.

$$X = -x_0 + \sum_{i=1}^{w-1} x_i 2^{-i} \tag{5}$$

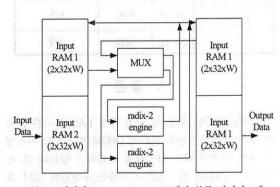

DIF FFT 연산에서 회전 인자 값으로써 사용되는 계수의 구성방식은 ROM 테이블에 cosine과 sine값을 구성하여 radix 엔진에서 출력되는 신호 값과 연산될 수있도록 구성하였고 radix engine은 radix-2 버터플라이구조를 이용하였으며 입력과 출력에 각각 2개씩의RAM 버퍼를 두어서 연속된 데이터의 입력을 저장함과 동시에 입력되는 데이터를 실시간으로 처리할 수있도록 구성하였다.

그림 5. 설계된 64-point FFT 프로세서 블록 다이어그램

이와 같은 설계 방식을 적용해서 구성한 FFT 프로세서의 전체 블록 다이어그램은 그림 5와 같으며 그림 6은 설계된 SIC 구조의 64-point FFT 프로세서를 나타내고 있다.

그림 6. 설계된 SIC 구조의 64-point FFT 프로세서

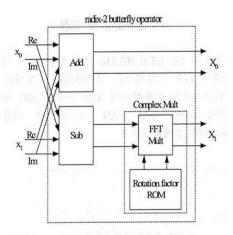

그림 7 버터플라이 연산은 2 개의 병렬로 연결된 radix-2 엔진에 의해서 연산이 이루어지며 입력된 데이터가 출력 RAM 버퍼에 저장되기 전에 각각의 radix-2 연산 단계마다 6번씩 처리된다.

그림 7. radix-2 버터플라이 연산자 블록도

그림 8. 설계된 radix-2 버터플라이 연산자

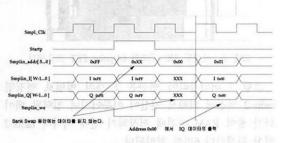

그림 8은 설계된 radix-2 버터플라이 연산자를 합성 한 그림이다. 그림 9는 출력 RAM 버퍼에 의해서 처리되는 신호들의 타이밍도를 보여주고 있다. 그림 9에서 알 수 있는 것처럼 출력 RAM 버퍼는 샘플 클럭 Smpl\_Clk에 의해서 작동을 하기 때문에 인가되는 출력 어드레스와 출력 데이터 사이에는 한 주기 정도의 지연에 의한 샘플 주기가 필요하게 된다.

그림 9. 출력신호에 따른 타이밍도

# Ⅳ. 모의실험 및 고찰

본 논문에서는 IEEE 802.11a 고속 무선 LAN 시스템에 적용할 FFT 프로세서를 설계하였다. 설계는 DIF FFT 알고리즘을 이용했으며 설계 구조는 SIC 구조를 이용하여 고속 무선 LAN 시스템에서 사용되는 64-point FFT 설계하였다.

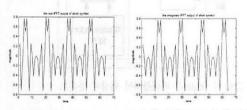

그림 10. Short sequence 값에 의한 IFFT 출력 파형

그림 11. Long sequence 값에 의한 IFFT 출력 파형

그림 10은 short sequence을 이용해서 수행된 결과이 며 이 결과에서 알 수 있는 것처럼 실수값과 허수값이 표준안에서 제안하고 있는 -1 < re, im < 1 사이에 존 재함을 확인하였으며 long sequence에 의해 수행된 결 과 또한 그림 11에서 볼 수 있는 것처럼 표준안을 만 족함을 확인하였다.

FFT 프로세서의 시뮬레이션을 위해서 Matlab을 통해서 64 point의 랜덤 벡터를 생성하였으며 이 랜덤 벡터는 설계 규격에서 설정하였던 QPSK 심볼에 맞도록 4개의 복소 성상도(complex constellation)를 갖는 QPSK 심볼로 결정하였다. 이는 벡터파일로 변환하여 Synopsys에 의해 불려진다.

IEEE 802.11a 고속 무선 LAN 시스템에 적용한 SIC 구조를 이용한 64-point FFT 프로세서에 대한 모의 실험 결과이다. 그림에서 Startp 신호가 수행되면서 입력 RAM 버퍼에 데이터가 저장되고 Sampling input write enable 신호에 의해서 입력 램 버퍼가 swapping을 일으킴을 확인할 수 있었다. 입력 신호에 의해 생성된 출력신호이다.

그림에서와 같이 설계된 SIC 구조의 FFT 프로세서가  $2.8~\mu$ s에서 데이터가 처리되어 출력되므로써 파이프 라인 구조의 고속 무선 LAN 시스템의 처리속도인  $3.6~\mu$ s 보다도  $0.8~\mu$ s 성능이 향상됨을 알 수 있었으며 표준안에서 제시하고 있는 FFT 프로세서의 연산처리시간인  $3.2~\mu$ s를 만족함을 확인하였다. 표 3은 설계된두 프로세서에 대한 비교 설명이다.

표 3. 파이프 라인 구조와 SIC 구조의 비교

|                    | 처리<br>속도 | 사용된<br>게이트 수 | 사용된<br>버터플라이 수 |

|--------------------|----------|--------------|----------------|

| 파이프라인구조<br>(R2SDF) | 3.6 μs   | 80K          | 6711           |

| SIC 구조             | 2.8 μs   | 60K          | 2개             |

# V. 결론

유럽형 디지털 방송 및 고속 무선 LAN과 같은 고속 의 멀티미디어 통신을 위하여 OFDM 변·복조 시스템에 대한 연구가 매우 활발하게 진행되고 있는데 본 논문에서는 OFDM 변·복조 시스템을 구현함에 있어 요구되는 FFT 프로세서에 대해서 기존 FFT 프로세서를 구현하기 위해서 가장 많이 사용되던 파이프라인 구조의 FFT 프로세서 방식을 대신해서 처리속도의 향상및 소비전력의 감소를 위해 SIC 구조를 적용한 64 point SIC FFT 프로세서를 설계하였다. 반면에 적용된 SIC 구조를 이용한 SIC FFT 프로서세는 하드웨어 설계가 약간은 복잡하지만 표준안에서 정의된 3.2 $\mu$ s보다 0.4 $\mu$ s 더 빠른 2.8 $\mu$ s안에 입력된 데이터를 처리함으로써 빠른 연산처리를 필요로 하는 고속 무선 LAN 시스

템에 적합한 구조임을 확인하였고 처리 단계 수를 4단계 줄여 줌으로써 소비 전력면에서도 파이프라인 FFT 프로세서에 비해서 우수함을 확인하였다

강 정 용(Jung-yong Kang) 정회원 한국통신학회 제 29권 12A호 2004년 12월호 참조

### 참 고 문 헌

- [1] IEEE 802.11a/D50, "High Speed Physical Layer in the 5GHz Band", 1999

- [2] Johan Melander, "Design of SIC FFT Architectures", Linkoping Studies in Science and Technology, No 618, Linköping University Sweden, May 1997

- [3] ISO 8802-11/D10, "Wireless LAN Medium Access Control(MAC) and Physical Layer(PHY) Specifications", Jan. 1999

- [4] Erling H Wold, Alvin M. Despain, "Pipeline and Parallel-Pipeline FFT Processing for VLSI Implementations", IEEE Transactions on computers, Vol C-33, No. 5, May 1984

- [5] Alan V. Oppenheim, Ronald W Schafer, "Discrete-Time Signal Processing", Prentice Hall Signal Processing Series

이 선 근(Seon-keun Lee) 정회원 한국통신학회 제 29권 12A호 2004년 12월호 참조