# 협대역 통신시스템을 위한 전처리기-등화기 구조의 FIR 여파기 설계

정회원 오 혁 준\*, 안 희 준\*\*

# Design of FIR Filters with Prefilter-Equalizer Structure for Narrowband Communication Systems

Hyukjun Oh\*, Heejune Ahn\*\* Regular Members

유 약

본 연구는 협대역 통신시스템을 위한 전처리가등화기 구조의 여파기에서, 곱셈기를 사용하지 않는 최소 복잡도의 디지털 FIR 여파기를 설계하는 방법을 제안한다. 제안하는 여파기는 순환 다항식(cyclotomic polynomial, CP) 여파기와 2차 내삽 다항식(interpolated second order polynomial, ISOP) 등화기로 구성되며, 이 두 여파기가 동시에 혼합 정수 선형 계획법mixed integer linear programming (MILP))으로 최적 설계되어 최소의 복잡도를 갖는 특성을 갖게 된다. 제안된 방식으로 설계된 여파기들은, 설계 규격을 만족하면서도 기존의 여파기에 비하여 복잡도면에서 월등히 간단함을 확인하였다.

**Key Words:** Digital filter, Narrowband communication, FIR, Cyclotomic polynomial, Prefilter, Equalizer, Interpolated second order polynomial

#### **ABSTRACT**

Optimal methods for designing multiplierless minimal complexity FIR filters with cascaded prefilter-equalizer structures are proposed for narrowband communication systems. Assuming that an FIR filter consists of a cyclotomic polynomial(CP) prefilter and an interpolated second order polynomial(ISOP) equalizer, in the proposed method the prefilter and equalizer are simultaneously designed using mixed integer linear programming(MILP). The resulting filter is a cascaded filter with minimal complexity. Design examples demonstrate that the proposed methods produce a more computationally efficient cascaded prefilter-equalizer than other existing filters.

# I . 서 론

무선 이동통신의 급속한 발전에 따라 원하는 대역에서 무선 신호를 추출하거나 원하는 대역 특성을 갖도록 무선 신호를 만들어 주는 것 등이 매우중요하게 대두되었다. 특히, 근래에 들어 고속의 데이터 전송 속도가 요구되면서 효율적인 주파수 대

역 이용을 위하여 주파수 대역을 여러 협대역으로 나누어 사용하는 다중 캐리어 변조 방식이 각광받고 있다. 무선 통신에서 또 다른 한 가지 큰 기술적 흐름은 소프트웨어 라디 & software defined radio) 로써, 중간 주파수단에서 샘플링을 시도하는 것이 기지국 쪽에서는 일반적인 방식으로 받아들여지고 있다. 이러한 중간 주파수 대역에서의 샘플링은 원

<sup>\*</sup> 광운대학교 전자통신공학과 (hj\_oh@kw.ac.kr) \*\* 서울산업대학교 제어계측공학과 (heejune@snut.ac.kr), 논문번호: KICS2005-01-002, 접수일자: 2005년 1월 3일

<sup>※</sup> 본 연구는 2004~2005년 서울산업대학교 산학중점대학사업 기술연구과제로 수행되었습니다

하는 신호가 협대역으로 나타나는 협대역 추출 시 스템이 된다. 일반적으로 이러한 협대역 여파기들은 매우 높은 복잡도를 요구하므로 저전력의 간단한 여파기가 필수적이다11.

성능 면에서 효과적이면서도 복잡도가 적은 간단 한 협대역 FIR 여파기를 설계하는 방법으로 전처리 기(prefilter)와 등화기(equalizer)를 연결한 직렬구조 설계방법이 있다[1-9]. 이 구조에서 전처리기는 정 지대역의 신호를 제거하고 등화기는 통과대역에서 의 규격을 만족하도록 설계한다 이때 전처리기는 일 반적으로 복잡도를 줄이기 위하여 내삽여파기 -41. 재귀러닝 함(recursive running sum: RRS)[5-8]. cyclotomic 다항식(CP) [9]등이 주로 사용된다 이 전 처리기의 설계 방법들은 대부분 임시방편적(Mad hoc) 방법[2-9]들이 사용되고 등화기는 Parks-McClellan 알 고리듬 선형 계획법 또는 진보된 최적화 기법이 사용된대[10-12].

기존의 연구방법은 전처리 여파기와 등화기로 구 성된 2단 구조에서, 각 전처리기와 등화기가 각각 따로 최적 설계되었다. 그러나 각각이 최적으로 설 계되었다 할지라도 전체적으로 동시에 최적 설계된 것이 아니므로 이렇게 설계된 여파기가 최적이라고 는 이야기 할 수 없다 두 여파기가 같은 조건 하에 서 동시에 최적 설계될 수 있다면 가장 적은 복잡 도를 갖는 최적의 여파기가 될 수 있을 것이다 이 런 관점에서 본 논문에서는 2차 내삽 다항식interpolated 2nd order polynomial)을 사용한 등화기를 제안하고 이를 CP 전처리기와 동시에 최소 복잡도 를 갖도록 최적 설계하는 선형계획법을 제안한다 시스템의 복잡도를 최소화하기 위하여 {-1,0,1} 의 계수를 갖는 CP와 canonic signed digit (CSD)1) 를 갖는 ISOP만으로 제한하여 설계한다

#### Ⅱ. 직렬 여파기의 선형 계획법 설계기법

일반적으로 pole과 zero를 갖는 디지털 여파기들은 모두 all zero여파기와 all pole 형태의 단위 여파기 들로 분해할 수 있다 이와 같이 구성된 유한 단위여 파기 공간  $\Omega$ 으로부터 적합한 여파기들을 선택하여 아래와 같은 직렬구조의 여파기를 설계할 수 있다.

$$H(z) = k \cdot \prod_{i=1}^{L} B_i(z)^{l_i}$$

$$\tag{1}$$

$H(z) = k \cdot \prod_{i=1}^{L} B_i (z)^{l_i}$

이 식에서 k는 상수이고  $B_{\epsilon}(z)$ 는 여파기 공간  $\Omega$ 상의 원소 $(B_i(z) \in \Omega)$ , L은  $\Omega$  공간상의 단위 여 파기의 수, 나는 동일한 성분 여파기의 수를 의미하 는 0 이상의 정수이다 이때 설계목표는 함수공간  $\Omega$ 이 적절히 주어졌을 때 시스템 응답 H(z)이 주 어진 주파수 응답 규격을 만족하면서 최소의 복잡 도를 갖도록 하는 여파기를 설계하는 것이다.여기 서 복잡도에 대한 척도로는  $B_i(z)$ 를 구현하는데 사용되는 곱셈 연산의  $(\pi e^m)$ , 덧셈연산의  $(\pi e^a)$  그 리고 지연 연산의  $4 (e^d)$ 의 함수

$$O_i = e_i^m + c_a \cdot e_i^a + c_d \cdot e_i^d \tag{2}$$

로 정의하겠다. 여기서  $c_a$ 과  $c_d$ 는 각기 덧셈 연산과 지연 연산의 복잡도의 곱셈연산의 복잡도에 대한 상대 가중치이다 이제 필터 설계문제를 정리하면 식(3)과 같다. 이 식에서  $\delta_n$ 과  $\delta_s$ 는 각각 통과대역과 저지대역의 허용오차이고  $H_{\ell}(\omega)$ 는 기준 주파수 응 답이다. 여기서 직렬 구조의  $|H_d(\omega)|$ 의 비선형적인 특성으로 인하여 비선형 최적화 방식을 필요로 한 다. 식 (3)의 조건을 로그 함수를 사용하여 dB 단 위로 정리하면

$\label{eq:minimize} \text{minimize } \sum_{i=1}^{L} \ l_i \cdot \textit{O}_i \qquad \text{(measure of complexity)}$ subject to  $||H(\omega)| - H_d(\omega)| < \delta_n$ (in passbands)  $|H(\omega)| < \delta_{c}$ (in stopbands) (3)

$$H_{dB}(\omega) = 20\log|H(\omega)|$$

$$= k_{dB} + \sum_{i=1}^{L} l_i \cdot B_{i,dB}(\omega)$$

(4)

로 변환할 수 있고 이는 식 (5)과 같은 MILP 문제 로 정리할 수 있다 여기서  $k_{dB} = 20 \log |k|$ ,  $B_{i,dB}(\omega)$  $=20\log|B_i(\omega)|$ 이다.

따라서 L이 매우 크지 않은 범위에서는  $k_{dB}$ 과  $l_i$ 를 변수로 하는 MILP 방법으로 원하는 여파기를 동시에 최적 해결할 수 있다

식 (5)로 주어지는 MILP 모델은 제한식의 일반 화를 통해 다양한 응용 분야로 확장되어 적용할 수 있다. 예를 들어, FIR 여파기를 사용하는 경우에도 여파기의 복잡도를 줄이기 위하여 비대칭FIR 여파 기를 사용하는 경우가 있다 이러한 경우엔 선형 위 상 특성에 가급적 근접하면서도 적은 복잡도의 여

<sup>1)</sup> CSD 상수는 2의 누승 계수의 합과 차로만 표시되는 계수

파기의 설계가 중요하다 직렬연결 여파기의 전체 그룹지연 응답은 각각의 단위 여파기들의 그룹지연 응답들의 합이므로 다음과 같은 제한조건의 추가를 통하여 통과대역에서 선형 위상 특성에 가장 근접 한 최적의 가단한 여파기를 얻을 수 있다

$$\left|\sum_{i=1}^{L} G_i^B(w) - G_d\right| \le \epsilon \tag{6}$$

여기서  $G_i^B(w)$ 는 단위 여파기  $B_i(z)$ 의 그룹지연 응답이다.

또 다른 매우 유용한 응용 분야는 이미 존재하는 다른 여파기  $H_{given}(w)$ 와 연결되어 설계하는 경우로써, 여러 블록이나 시스템이 연결된 경우에 유용하다이런 경우 식 (7)과 같은 간단한 제한조건의 추가로 최소의 복잡도를 갖는 여파기를 설계할 수 있다

$$|H_{aiven,dB} + H_{dB}| < 20\log\left(H_d(w) + \delta\right) \tag{7}$$

또한 제안된 방식은 다중 캐리어 전송시스템에도 적용이 가능하다 다중 캐리어 전송시스템에서는 부전송파의 상호간섭을 최소화 하는 것이 중요하다이 간섭은 결국 프로토타입 여파기의 정지대역 에너지 제거율과 관련되어 있다 즉, 제안된 직렬연결여파기의 전체 정지대역 에너지 제거율은 각각의단위 여파기들의 정지대역 에너지 제거율들의 곱과비례하게 된다. 따라서 각각의 단위 여파기들의 정지대역 에너지 감쇄율의 로그 값의 합을 이용하여원하는 상호부전송파 간섭 제거율을 얻을 수 있는프로토타입 여파기의 설계가 가능하다

$$\sum_{i=1}^{L} e_{i,dB}^{B} \le \epsilon_{s} \tag{8}$$

여기서  $e^B_{i,dB}$ 는 단위 여파기  $B_i\left(z\right)$ 의 정지대역 에너지 감쇄율의 로그 값이다

# Ⅲ. 전처리기-등화기 구조를 갖는 연쇄 FIR 여파기의 설계 절차

CP 전처리기는 전처리기의 목적인 정지대역의 신

호 감쇄를 효과적으로 얻을 수 있으나 다른 전처리기와 같이 통과대역 상의 단조감쇄 현상을 발생시키는 문제점이 있다 따라서 전처리기의 후미에 위치하는 등화기는 이 감쇄를 보상하도록 설계되어야한다. 이러한 기능을 수행하는 방법으로써 통과대역에서 위로 볼록한 모양의 주파수 응답 특성을 갖는 다항함수 E(z)를 사용하는 방법이 있다 설명을위하여, [9]에서 사용된바 있는 다음과 같은 응답특성을 갖는 대역통과여파기의 설계를 예로 들어보겠다.

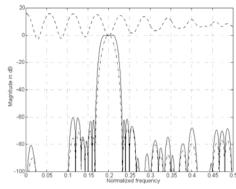

그림 1의 일점쇄선은 설계된 CP 전처리기의 주 파수 응답을 보여준다 주목할 점은 전처리기에 의 한 통과대역 단조감쇄가 약 8dB라는 점이다. 한편 그림 1의 끊어진 선은 설계된 등화기의 주파수 응 답을 보여주고 있는데 앞서 설명한 바와 같이 통과 대역에서 볼록한 형태의 응답 특성을 갖고 있어서 전처리기에 의한 8dB 감쇄를 보상할 수 있다 그림 1의 실선 응답에서 알 수 있듯이 결국 최종응답은 주어진 설계요구 사항을 만족하고 있다 다음절에 설명할 ISOP는 통과대역 상에 위로 볼록한 주파수 특성을 갖도록 조정할 수 있는 특성을 가지고 있다 제안된 전처리가등화기 구조의 설계를 위한 단위 여파기의 집합  $\Omega$ 은 각기 전처리기와 등화기에 해당 하는 두 집합  $\Omega_1$ 과  $\Omega_2$   $(\Omega = \Omega_1 \cup \Omega_2)$ 로 분할할 수 있다.  $\Omega_1$ 의 원소들은 CP를 정리하여 얻을 수 있고  $\Omega_2$ 의 원소는 ISOP로부터 얻을 수 있다

그림 1. 전처리가-등화기 구조의 대역 통과 여파기 주파수응답: 전처리기 (일점쇄선), 등화기 (끊어진 선), 전체 여파기 (실선)

passband  $f \in [0.189, 0.211]$  (9) stopband  $f \in [0, 0.168] \cup [0.232, 0.5]$  ripple  $\delta_{p,dB} \le 0.25dB$  (in passband),  $\delta_{s,dB} \le -60dB$  (in stopband) (12),  $\delta_{n,dB} = 20\log(1 - \delta_n)$ ,  $\delta_{s,dB} = 20\log\delta_s$ )

#### 3.1 CP 전처리기

곱셈기 없는 전처리기를 설계하기 위하여  $\{-1,0,1\}$ 만을 계수로 사용하는 CP을 고려하면 모두 104개가 존재한다. 이 CP들의 근은 모두 z-평면상의 단위원 위에 존재한다.

집합  $\Omega_1$ 는 주어진 설계 규격을 만족할 수 있고 구현 복잡도가 적은 $\mathbf{CP}$ 들로만 구성 한다. 두 개 이 상의  $\mathbf{CP}$ 로 구성된 직렬 구조의 새로운 여파기 역시 하나의 새로운 단위 $\mathbf{CP}$  여파기 역할을 할 수 있다. 예를 들어  $C_5(z)=(1-z^{-5})/(1-z^{-1})$ 과  $C_{10}(z)$ =  $(1+z^{-5})/(1+z^{-1})$ 을 고려하면.

$$C_{5}(z) C_{10}(z) = \left(\frac{1-z^{-5}}{1-z^{-1}}\right) \left(\frac{1+z^{-5}}{1+z^{-1}}\right)$$

$$= \left(\frac{1-z^{-10}}{1-z^{-2}}\right)$$

(10)

로 표현되므로,  $C_5(z)$ 과  $C_{10}(z)$ 의 연결조합은 두개의 덧셈이 절약된  $(1-z^{-10})/(1-z^{-2})$ 로 구현된다. 최종적으로 전처리기 P(z)의 시스템 응답은

$$P(z) = \prod_{q=1}^{Q} F_q(z)^{m_q}$$

(11)

으로 표현된다. 이 식에서  $F_q(z)\in\Omega_1$ 이고,  $m_q$ 는 양의정수, Q는  $\Omega_1$ 의 총 원소의 개수이다. 설계 규격 만족을 위하여  $F_q(z)$ 의 해는 정지대역 또는 전이대역(transition band) 안에 위치하여야 한다

#### 3.2 ISOP 등화기

ISOP는 다음 선형 위상응답 특성을 갖는 대칭 계수 2차 내삽 다항식으로 구성된다

$$S(z)=(a+bz^{-1}+az^{-2})$$

(12) (a과 b는 CSD 계수,  $b^2-4a^2>0$ ,  $a\neq 0$ )

ISOP은

$$S^{I}(z) = (a + bz^{-I} + az^{-2I})$$

(13)

로 정의되는 다항식이다 주파수 응답은  $S^{I}(z)$ 은

$$|S^{I}(\omega)| = |b + 2a \cdot \cos I\omega| \tag{14}$$

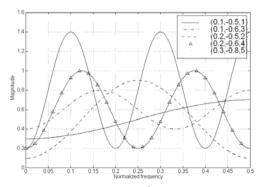

그림 2. 변수 (a,b,I)에 따른  $|S^I(\omega)|$ 의 파형.

로 표현된다. 여기서 I는 내삽 비중치  $b^2-4a^2>0$  이고  $a\neq 0$ 인  $|S^I(\omega)|$ 은 그 주파수 크기 응답이 변수 (a,b,I)를 조절함으로써 쉽게 조정이 가능한 삼각파형이 된다. 결과적으로, 주어진 여파기 조건에서 통과대역 상에 위로 볼록한 형태를 갖는 $|S^I(\omega)|$ 을 구할 수 있다. 예를 들면, 그림 2의 5개의  $|S^I(\omega)|$  중에서, 통과대역이  $f\in[0,0.2]$ 로 주어졌을 경우 (a,b,I)=(0.1,-0.5,1)과 (0.2,-0.5,2)두개의 ISOP가 등화기의 역할로 적합하다는 것을 알 수 있다.

다음으로, 변수 (a,b,I)를 선택하는 방법을 설명한다.  $|S^I(\omega)|$ 의 통과대역에서 위로 볼록한 특성을 유지하기 위하역,  $|S^I(\omega)|$ 는 통과대역 상에 한 개보다 적은 극점을 갖아야 하는데 이 특성은 변수 I 값의 조절을 통하여 가능하다

관찰 I) 시스템 주파수 응답 $|S^I(\omega)|$ 은

$$1 \le I \le \frac{2\pi}{\omega_B} \tag{15}$$

인 조건하에서, 통과대역에서 하나이상의 극점을 가질 수 없다. 단,  $\omega_B$ 는 저역 여파기의 경우에는 대역 폭의 두 배, 또는 일반적 통과대역의 경우에는 대역 폭의 크기이다.

증명)  $|S^I(\omega)|$ 의 두 인접한 극점사이의 거리는  $2\pi/I$ 로 주어진다 따라서  $\omega_B$ 는  $2\pi/I$ 보다 작으면, 그 대역 내에 극점을 하나 이상 갖지 않는다

$S^I(z)$ 의 근이 z-평면상의 단위원에 있지 않는 것이 바람직하다 왜냐 하면, 단위원 위에  $S^I(z)$ 의 근이 있는 경우  $S^I(z)$ 는 zero를 갖게 되어 통과대역 상에 z0에 마네를 만드는 일종의 z0이로 적합하지 않다 z0이 근이 단위원상에 존재하지 않으면 z0이 근위원상에 존재할 수가 없으므로 2차 방정식의 판별식을 이용하면 z10인 경우에 단위원상에 근을 갖지 않는다중근인 경우에 단위원 상에 근을 가지게 된다

ISOP의 변수 a와 b는 CSD 계수이므로, ISOP는 덧셈기, 쉬프터, 지연기만으로 구현할 수 있다 ISOP는 a와 b의 유한 어장과 각(15)에 따라 그 수가 유한하므로 유한 단위 여파기 공간을 이룬다 ISOP의 집합  $\Omega_2$ 는 각 원소들의 여러 가지 시간상 주파수 상의 특성을 고려함으로써 그 크기를 더 줄일 수가 있다. 예를 들어, 여러 ISOP들이 유사한 주파수 응답을 보이는 경우, 하나만을 남기고 나머지를 제외시키거나, 너무 평탄한 통과대역 응답을 갖는 것을 제외한다.

ISOP 등화기는 단위 ISOP들의 직렬연결로 구성 된다. 이때 시스템 함수는

$$E(z) = \prod_{r=1}^{R} S^{I_r}(z)^{n_r}$$

$$= \prod_{r=1}^{R} (a_r + b_r z^{-I} + a_r z^{-2I})^{n_r}$$

(16)

로 표현된다. 여기서  $S^L(z) \in \Omega_2$ ,  $n_r$ 는 양의 정수,  $a_r$ 과  $b_r$ 는 CSD 계수, R은  $\Omega_2$ 의 원소수이다

3.3 CP 전처리기와 ISOP 등화기의 동시 설계 일반적인 경우의 CP 전처리기와 ISOP 등화기의 동시설계방법은 제2절에 소개되었다. 이때 전체 시스템 응답 함수 H(z)은

$$H(z) = k \cdot P(z)E(z)$$

$$= k \cdot \prod_{q=1}^{Q} F_{q}(z)^{m_{q}} \prod_{r=1}^{R} S^{L_{r}}(z)^{n_{r}}$$

(17)

과

$$H_{dB}(\omega) = k_{dB} + \sum_{q=1}^{Q} m_q F_{q,dB}(\omega) + \sum_{r=1}^{R} n_r S_{r,dB}^{I}(\omega)$$

(18)

로 주어진다 여기서  $k_{dB}=20\log|k|,\;\;F_{q,dB}(\omega)=20\log|F_q(\omega)|,S^{I_{dB}}(\omega)=20\log|S^I(\omega)|$ 이다. 본 논문에서 사용하는 CP와 ISOP는 모두 곱셈을 사용하지 않기 때문에, 식 (5)의 계산 복잡도는

$$\sum_{q=1}^{Q} m_q \cdot (e_q^a + c \cdot e_q^d) + \sum_{r=1}^{R} n_r \cdot (e_r^a + c \cdot e_r^d)$$

(19)

이 된다. 이 식에서  $e_q^a$   $(e_r^a)$ 과  $e_q^d$   $(e_r^d)$ 은 각 단위 여파기  $F_q(z)$   $(S_r^I(z))$ 의 덧셈연산과 지연연산의 수이고, c는 각기 덧셈과 지연의 복잡도에 따른 가중치이다. 따라서 CP 전처리기와 ISOP 등화기로 구성되는 최소의 복잡도를 갖는 직렬연결 여파기는 식(18), 식 (19)과 제 II 장에 제안한 MILP 모델을통하여 CP 전처리기와 ISOP 등화기를 동시에 최적설계하여 얻을 수 있다

#### IV. 설계 예

본문에서 제안된 전처리가등화기 구조의 여파기와 기존의 여파기들의 비교를 위하여 참고 문헌 [1], [5], [9]에서 사용된 저대역 여파기 설계와 참고문헌 [5], [6], [9]에서 사용된 대역 통과 여파기에 제안된 방법을 적용하여 설계하였다 기존의 여파기들은 부동 소수점 계수를 갖는 여파기로 설계되어 실제 구현할 때에는 훨씬 더 큰 복잡도를 갖게 되는 반면, 제안된 여파기는 이미 모두 고정수수점 계수로 설계되었으므로 실제 구현할 때 추가되는 복잡도는 없다 식 (19)의 상수 c는 0.5로 선택하였다. 본 논문에서 MILP문제를 효과적으로 풀기위하여 소프트웨어 라이브러리 CPLEX[13]를 사용하였다

설계 예 1(저대역 통과 여파기) 정규화 주파수응답 규격은

passband

$$f \in [0,0.021]$$

stopband  $f \in [0.07,0.5]$

ripple  $\delta_{p,dB} \leq 0.1dB$  (in passband), (20)

$\delta_{s,dB} \leq -60dB$  (in stopband.)

이 주어진 설계규격 하에서 13개의 유효한 단위 CP가 선택되었고, 그들의 결합 중에서 20개가 더

선택되었다. CP 전처리기를 위한 집합  $\Omega_1$ 는 총 33 개의 다항식으로 구성이 된다 즉, Q=33. 또한 식 (15)의 조건은  $1 \le I \le 23$ 이 되고, 식 (15)를 만족하는 230개의 ISOP가 존재한다. 주파수 응답특성을 고려하여 이들 중 일부를 제거하고 나면72개의 원소를 갖는  $\Omega_2(R=72)$ 가 얻어진다. 최적 설계된 최종 전처리기와 등화기는

$$P(z) = (1+z^{-3})(1+z^{-4})^{2}(1+z^{-6})$$

$$\left(\frac{1-z^{-10}}{1-z^{-1}}\right)\left(\frac{1-z^{-13}}{1-z^{-1}}\right)\left(\frac{1-z^{-14}}{1-z^{-1}}\right)$$

$$E(z) = (2^{-3}-2^{-1}z^{-4}+2^{-3}z^{-8})^{2}$$

$$(2^{-3}-2^{-1}z^{-6}+2^{-3}z^{-12})$$

(21)

이다.

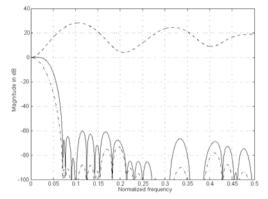

그림 3. 예제 1의 CP 전처리기 주파수 응답 (일점쇄선), ISOP 등화기 응답 (끊어진 선), 전체 응답 (실선)

그림 3은 설계된 전체 여파기의 주파수 응답이 주어진 조건을 잘 만족하고 있음을 보여 준다 표 1은 전체 여파기  $H(z) = k \cdot P(z)E(z)$ 의 계산 복잡도를 기존의 설계방법들과 비교한 것이다 괄호에 표시된 곱셈기는 상수 k를 의미하며, 실제 곱셈기로 여겨지지 않을 수도 있다. 설계된 CP 전처리기

-ISOP 등화기는 상수 k를 제외하면 단지 16개의 덧셈과 82개의 지연연산으로만 구현할 수 있다 따라서 본 논문에서 제안된 여파기가 기존의 다른 여파기들에 비하여 구현이 훨씬 간단함을 확인할 수 있다.

설계 예 2(대역 통과 여파기) 이 예에서 사용된 정 규화 주파수응답 규격은 식(9)을 사용한다.

15개의 유효한 단위 CP가 계산되었고, 이들의 조합들 중에서 25개가 더 선택되었다. 결국 CP 전처리기에 대한 집합  $\Omega_1$ 은 40개의 CP 다항식으로 구성되었다, 즉 Q=40이다. 식 (15)으로부터  $1\leq I\leq 45$ 이 계산되고, 식 (15)를 만족하는 450개의 ISOP가 계산되었다. 앞서와 마찬가지로 이들의 주파수특성을 고려하여 비슷한 응답을 보이거나 평평한응답을 보이는 것들을 제외하고 나면 $\Omega_2$ 는 38개의원소를 갖게 된다 (R=38). 결국, 제안된 전처리가등화기 전체 시스템은

$$P(z) = (1 - z^{-2})(1 - z^{-3})$$

$$\cdot (1 - z^{-2} + z^{-4})^{2} (1 + z^{-5})$$

$$\cdot (1 - z^{-3} + z^{-6})^{2}(1 - z^{-7})$$

$$\cdot (1 + z^{-10})(1 + z^{-5} + z^{-10})$$

$$\cdot (1 + z^{-15})$$

$$\cdot (1 + z^{-15})$$

$$\cdot (1 + z^{-10} + z^{-15} + z^{-20} + z^{-30})$$

$$E(z) = (2^{-3} + 2^{-1}z^{-17} + 2^{-3}z^{-34})$$

$$(2^{-3} + 2^{-1}z^{-18} + 2^{-3}z^{-36})$$

$$(22)$$

로 구해진다. 그림 1은 설계된 시스템의 주파수 응답이 주어진 규격을 잘 만족하고 있음을 보여 준다제안된 CP 전처리기-ISOP 등화기 시스템은 단지 24개의 덧셈과 172의 지연으로 구성된다 또한 표 2에서 볼 수 잇듯이 기존의 여파기들에 비해 월등히 복잡도가 작음을 알 수 있다

표 1. 제안된 여파기와 기존 설계방법의 여파기의 계산 복잡도 비교(설계 예 1)

|      |       |     |       | СР    |       |

|------|-------|-----|-------|-------|-------|

|      | 변형    |     | CP    | 전처리기와 | CP    |

|      | K-H와  | 내삽  | 전처리기와 | 부집합   | 전처리기와 |

|      | Remez | FIR | Remez | 선택    | ISOP  |

|      | 등화기   | 여파기 | 등화기   | 등화기   | 등화기   |

|      | [5]   | [1] | [9]   | [9]   |       |

| 곱셈연산 | 17    | 5   | 10    | 4     | (1)   |

| 덧셈연산 | 37    | 15  | 28    | 16    | 16    |

| 지연연산 | 73    | 78  | 71    | 85    | 82    |

|      |                             |                                |                              | СР                      |                      |

|------|-----------------------------|--------------------------------|------------------------------|-------------------------|----------------------|

|      | 변형                          |                                | CP                           | 전처리기와                   | CP                   |

|      | K-H와<br>Remez<br>등화기<br>[5] | Cabezas<br>Diniz<br>설계2<br>[6] | 전처리기와<br>Remez<br>등화기<br>[9] | 부집합<br>선택<br>등화기<br>[9] | 전처리기와<br>ISOP<br>등화기 |

|      |                             |                                |                              |                         |                      |

|      |                             |                                |                              |                         |                      |

|      |                             |                                |                              |                         |                      |

| 곱셈연산 | 43                          | 7                              | 17                           | 13                      | (1)                  |

| 덧셈연산 | 163                         | 48                             | 58                           | 49                      | 24                   |

| 지연연산 | 162                         | 217                            | 161                          | 180                     | 172                  |

표 2. 제안된 여파기와 기존 설계방법의 여파기의 계산 복잡도 비교(설계 예 2)

# Ⅴ. 결 론

본 논문에서는 협대역 통신 시스템을 위한 전처리가-등화기구조의 시스템에서, 최소의 복잡도를 갖도록 하는 곱셈기 없는 여파기를 설계하였다 제안된 여파기는 CP 전처리기와 CSD 계수만을 갖는 ISOP 등화기로 구성되는 여파기로써 동시에 최적화되어 전체 직렬연결 여파기의 복잡도가 최소화 되도록 설계되었다.

또한, 제안된 여파기가 최소의 복잡도를 가짐을 예제를 통하여 확인할 수 있었다 본 연구에서 제안 된 방법의 확장으로는 설계에 사용될 수 있는 또다른 다항식을 고안하는 것을 생각할 수 있다

#### 참고문 헌

- [1] R. Lyons, "Interpolated narrowband lowpass FIR filters," IEEE Signal Processing Magazine, vol. 20, pp.50-57, Jan. 2003.

- [2] M. Wilbur, T. Davidson, and J. Reilly, "Efficient Design of Oversampled NPR GDFT Filterbanks," IEEE Trans. Signal Processing, vol.52, July 2004.

- [3] S. Netto, L. Barcellos, and P. Diniz, "Efficient Design of Narrowband Cosine-Modulated Filter Banks Using a Two-Stage Frequency-Response Masking Approach," Journal of Circuits, Systems, and Computers, vol. 12, pp. 1-12, Dec. 2003.

- [4] T. Saramaki, Y. Neuvo, and S. K. Mitra, "Design of computationally efficient interpolated FIR filters," IEEE Trans Circuits Syst., vol. 35, pp. 70-88, Jan. 1988

- [5] J. W. Adams and A. N. Willson, Jr., "Some efficient digital prefilter structure," IEEE

Trans. Circuits and Syst. vol. 31, pp. 260-265, Mar. 1984.

- [6] J. E. Cabezas and P. S. R. Diniz, "FIR Filters using interpolated prefilters and equalizers," IEEE Trans Circuits Syst., vol. 37, pp. 17-32, Jan. 1990.

- [7] K. Sivaramakrishnan, I. Linscott, and G. Tyler, "Design of Multiplierless Programmable Linear Phase Narrowband-Bandpass FIR Filters," IEEE Int. Symp. Circuits and Systems, vol 3, pp. 493-496, May 2004.

- [8] G. Jovanovic-Dolecek, V. Dolecek "Method for narrowband minimum phase filter design," Electronics Letters, vol. 37, pp. 324-325, Mar. 2001.

- [9] R. J. Hartnett and G. F. Boudreaux-Bartels "On the use of cyclotomic polynomial prefilters for efficient FIR filter design," IEEE Trans. Signal Processing vol. 41 pp. 1766-1779 May 1993.

- [10] H. Dam, K. Teo, S. Nordebo, and A. Cantoni, "The Dual Parameterization Approach to Optimal Least Square FIR Filter Design Subject to Maximum Error Constraints," IEEE Trans. Signal Processing, vol. 48, pp. 2314-2320, Aug. 2000.

- [11] Y. Lim, Y. Sun, and Ya Jun Yu, "Design of Discrete-Coefficient FIR Filters on Loosely Connected Parallel Machines," IEEE Trans. Signal Processing, vol. 50, pp. 1409-1416, June 2002.

- [12] D. Li, Y. Lim, Y. Lian, and J. Song, "A Polynomial-Time Algorithm for Designing FIR Filters With Power-of-Two Coefficients," IEEE Trans. Signal Processing, vol.

50, pp. 1935-1941, Aug. 2002.

[13] Using the CPLEX callable library and CPLEX mixed integer library, ILOG Inc. Mountain View, CA, 2005.

# 오 혁 준(Hyukjun Oh)

정회워

1995년~1999년 한국과학기술원 전기 및 전자공학과(공학박사) 1999년~2001년 미국 Stanford 대학 박사 후 과정

2001년~2004년 미국 Qualcomm 사. 3GPP CSM/MSM 개발 현재 광유대학교 전자통신공학

과 (조교수)

<관심분야 차세대 이동통신, 통신 모뎀 SoC 설계, 통신 신호 처리 이론 및 설계, 통신 임베디드 시스템 응용

#### 안 희 준(Heejune Ahn)

정회워

1995년 3월~2000년 2월 한국과 학기술원 전기 및 전자공학과 (공학박사)

2000년 2월~2002년 8월 (주) LG 전자 차세대단말연구소 선임 연구워

2002년 9월~2004년 12월 (주)

Tmax Soft 기술연구소, J2EE WAS개발 팀장 책임 연구워

2004년 2월~현재 서울산업대학교 제어계측공학과 전 임강사

<관심분야> 통신 소프트웨어 구현 멀티미디어 인터넷 통신, 임베디드 시스템 응용