# A SiGe HBT Variable Gain Driver Amplifier for 5-GHz Applications

Kyu-Sung Chae\*, Chang-Woo Kim\* Regular Members

#### **ABSTRACT**

A monolithic SiGe HBT variable gain driver amplifier (VGDA) with high dB-linear gain control and high linearity has been developed as a driver amplifier with ground-shielded microstrip lines for 5-GHz transmitters. The VGDA consists of three blocks such as the cascode gain-control stage, fixed-gain output stage, and voltage control block. The circuit elements were optimized by using the Agilent Technologies' ADS. The VGDA was implemented in STMicroelectronics' 0.35 µm Si-BiCMOS process. The VGDA exhibits a dynamic gain control range of 34 dB with the control voltage range from 0 to 2.3 V in 5.15-5.35 GHz band. At 5.15 GHz, maximum gain and attenuation are 10.5 dB and -23.6 dB, respectively. The amplifier also produces a 1-dB gain-compression output power of -3 dBm and output third-order intercept point of 7.5 dBm. Input/output voltage standing wave ratios of the VGDA keep low and constant despite change in the gain-control voltage.

Key Words: SiGe, HBT, Variable Gain Driver Amplifier(VGDA), 5-GHz

## I. Introduction

Recently, frequencies in 5-GHz band are widely used for data transmission systems such as IEEE 802.11a and HIPERLAN II because they have advantage of high data transmission rate<sup>[1],[2]</sup>. In general, variable gain amplifiers(VGAs) are used to adjust the received-signal amplitude in receiver blocks or used to control the transmission signal power in transmitter blocks. For the transmitter, the variable gain driver amplifier(VGDA) which acts as a driver amplifier embedded in front of a power amplifier is an essential component to maximize the dynamic range of the overall system. Therefore, the VGA must have a wide gain control range, high dB-linear gain control ability, and high linearity.

There are several monolithic CMOS variable gain low noise amplifiers(VGLNAs)<sup>[3],[4]</sup> and VGAs combined with GaAs technology for 5-GHz wireless applications<sup>[5],[6]</sup>. The CMOS VGLNAs do

not simultaneously satisfy the wide gain control range, high dB-linear gain control and high linearity. On the other hand, the GaAs-based VGAs exhibit good performance, but they are relatively expensive. The low-cost ICs are required substantially since cost is of major concern for all wireless communication products. The high-performance and low-cost VGA can be implemented by advanced SiGe heterojunction bipolar transistor (HBT) technology. This technology also allows to use the CMOS circuits on the same substrate (system on chip), which reduces the production cost and provides high integration.

In this paper, we have developed a monolithic SiGe VGDA with a high dB-linear gain control and high linearity for 5-GHz wireless applications. The VGDA has been designed and fabricated by using ST Microelectronics' SiGe MMIC design library and 0.35-um Si-BiCMOS process. The on-wafer measurement was performed by using a RF probe station under single and two tone

논문번호 : KICS2005-10-411, 접수일자 : 2005년 10월 12일, 최종논문접수일자 : 2006년 3월 13일

<sup>※</sup> 본 연구는 경희대학교와 한국과학재단(특정기초연구 지원사업, 과제번호:R01-2003-000-10455-0)의 지원으로 수행 되었음.

<sup>\*</sup> 경희대학교 일반대학원 전파공학과(kschae@khu.ac.kr)

inputs. The measured results of the developed VGDA will be discussed.

## II. MMIC Design and Implementation

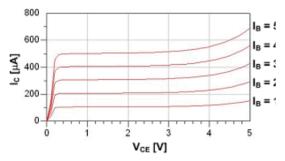

Fig. 1 shows I-V characteristics for an unit SiGe HBT with one-finger emitter area of 0.4  $\times$   $10\mu\text{m}^2$ . The HBT demonstrates a dc current gain of 100 with BV<sub>CEO</sub>= 5 V. In ST Microelectronics' technology, npn HBTs offer a peak  $f_t$  and  $f_{max}$  of 45 GHz and 60 GHz, respectively.

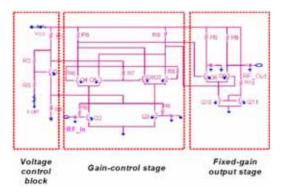

A simplified schematic of the VGDA designed in this work is shown in Fig. 2.

Fig. 1. Measured I-V characteristics for SiGe HBT

Fig. 2. A Schematic circuit diagram of the VGDA

The differential VGDA consists of variable and fixed gain stages in a cascade connection. The gain-control stage based on the Gilbert cell structure with good linearity provides the variable gain mechanism<sup>[7]</sup>. The gain control is achieved by varying the transconductance of  $Q_2$ - $Q_7$  through controlling of the base voltage( $V_{ctrl}$ ) of the voltage control block. The collector current of  $Q_1$  increases with  $V_{ctrl}$ , which leads to increase in base

voltages of  $Q_2$ - $Q_7$ . This results in an exponential increase in the transconductance of the HBT ( $Q_2$ - $Q_7$ ). Therefore, the gain of the HBT increases dB-linearly with  $V_{ctrl}$  since the gain of the HBT depends linearly on the transconductance in bipolar transistors.

The input-signal is sensed at bottom differential pair ( $Q_2$  and  $Q_3$ ). The fixed-gain output stage acts as a fixed gain output buffer to amply the RF signal. This has been also designed so that the output VSWR keeps constant with varying the control voltage  $V_{ctrl}$  of the variable gain stage.

Using nonlinear RF circuit simulations with Agilent Technologies' Advanced Design System, all passive elements were optimized to obtain a gain-control range > 35 dB, 1-dB gain-compression output power( $P_{1-dB}$ ) > -1 dBm, and output-referred third-order intercept point(OIP<sub>3</sub>) > 10 dBm in 5-GHz band.

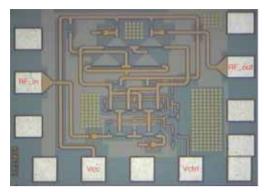

The **VGDA** implemented was Microelectronics' 0.35-μm Si BiCMOS process using SiGe HBTs and passive components. MIM capacitors and thin-film resistors provided from the ST Microelectronics' library were used. Also, in designing of the VGDA, ground-shielded microstrip lines were used in all transmission-line. The ground-shielded microstrip line is mainly composed of a 1 un-thick bottom SiO2 layer on low resistive silicon substrate, a 1µm-thick Al ground layer, a 2µm-thick SiO<sub>2</sub> layer, and a 2µm-thick top Al signal line layer in turn. The conventional structure has only one bare signal-line on top of the SiO<sub>2</sub> layer and silicon substrate. So the electric fields from the signal line are not shielded and some of them are caught by the low resistive substrate to be dissipated. On the other hand, in the ground-shield structure, most of the electric fields from the signal line are shielded by the ground metal layer so that it can not reach the leaky silicon substrate. Therefore, the radiation loss of signal and the isolation between the signal lines can be improved significantly. A microphotograph of the fabricated VGDA chip is shown in Fig. 3. The chip size is  $0.76 \times 0.74$  $mm^2$ .

Fig. 3. Microphotograph of the VGDA chip

## III. Experimental Results

For small and large signal measurements, the VGA chips were mounted on a probe station with RF connections made by 200  $\mu$ m pitch coplanar probes and DC biasing applied through a GPGPG probe. The results were measured with a vector network analyzer and spectrum analyzer connected to single-ended output 50-ohm port. The collector bias voltage of  $V_{CC}$  is 3.2 V and the control voltage can vary from 0 V to 2.5 V.

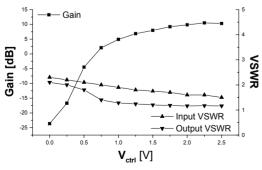

Fig. 4 shows the measured gain control and input/output VSWR performance at 5.15 GHz. The maximum gain of 10.5 dB is obtained at  $V_{ctrl}$  = 2.3 V, while the maximum attenuation is -23.6 dB at  $V_{ctrl}$  = 0 V. A dynamic gain control range of 34 dB is achieved by controlling  $V_{ctrl}$  with a range from 0.0 to 2.3 V.

In table 1, the measured gain control range of the VGA in this work is compared with that of other works<sup>[3],[5]</sup>.

Fig. 4. Small-signal gain and input/output VSWR characteristics of the VGDA as a function of  $V_{ctrl}$  at 5.15 GHz

Table 1. Comparison of gain control range

|                    | REF[3]         | REF[5]             | This work |

|--------------------|----------------|--------------------|-----------|

| process            | 0.18µm<br>CMOS | InGaP/GaA<br>s HBT | SiGe HBT  |

| gain control range | 8.9 dB         | 25 dB              | 34 dB     |

| control voltage    | 0-1.8 V        | 1-2 V              | 0-2.3 V   |

| frequency          | 5.7 GHz        | 5.25 GHz           | 5.15 GHz  |

From the table 1, it can be clearly seen that the SiGe HBT VGDA exhibits a wider gain-control range than the others.

The VGDA exhibits a gain-control sensitivity of 67 mV/dB. In general, a gain-control votage for 1-dB control in a bipolar transistor is much larger than a thermal voltage(26 mV/dB at the room temperature) in order to be insensitive to temperature variation.

The VGDA also exhibits a dynamic gain control range of 34 dB with a 0-2.3 Vdc voltage range in 5.15-5.35 GHz band. The input/output VSWR keeps low(< 2.2) and constant despite change in the gain-control voltage. The input/output return loss variations are less than 1-dB peak-to-peak over the gain-control range.

Fig. 5 shows the output power and third order output intercept point(OIP<sub>3</sub>) as a function of input power at 5.15 GHz with  $V_{ctrl}$ = 2.3 V. Two signals were applied to the VGDA at 5.150 and 5.155 GHz. Two-tone third order intercept point

Fig. 5. Output power and third-order intermodulation product (IMD3) as a function of input power at 5.15 GHz with  $V_{\rm cut}$ =2.3 V

IP<sub>3</sub> is determined to be -2.5 dBm at the input and 7.5 dBm at the output. The measured 1-dB gain compression output power of the VGDA is -3 dBm at 5.15 GHz. At attenuation condition, the OIP<sub>3</sub> degrades with decrease of V<sub>ctrl</sub>.

### IV. Conclusions

We have developed a monolithic 5-GHz band SiGe HBT variable gain driver amplifier with a high dB-linear gain control and high linearity. The VGDA archives a dynamic gain control range of 34 dB with a 1-dB gain-compression output power of -3 dBm and output third-order intercept point of 7.5 dBm at 5.15 GHz. Our work addressed one of major challenges for the implementation of fully monolithic transmitters using a standard silicon BiCMOS process.

#### REFERENCES

- [1] William J. McFarland, "WLAN System Trends and the Implications for WLAN RFICs," IEEE RFIC Symposium. pp. 141-144, June 2004.

- [2] A. Italia, L.La Paglia, A. Scuderi, F. Carrara, E. Ragonese, and G. Palmisano, "A Silicon Bipolar Transmitter Front-End for 802.11a and HIPERLAN2 Wireless LANs," IEEE J. Solid-State Circuits, vol. 40, no. 7, pp. 1451-1459, July 2005.

- [3] C.-H. Liao and H.-R. Chuang, "A 5.7-GHz 0.18-um CMOS gain-controlled differential LNA with current reuse for WLAN receiver," IEEE Microwave and Wireless Components Lett. Vol. 13, pp. 526-528, Dec. 2003.

- [4] M. Lin, Y. Li, and H. Chen, "A 5-GHz CMOS front-end circuit with low power, low noise and variable gain for WLAN applications," Proc. of Int'l Symp. on VLSI Tech. Sys. and Applications, pp. 280-283, Taiwan, Oct. 2003.

- [5] H. Dodo, Y. Aoki, N. Hayama, N. Fujii, and H. Hida, "A low-power and variable-gain transceiver front-end chip for 5-GHz-band WLAN applications," in IEEE MTT-S Int'l Microwave Symp. Dig., pp. 1559-1562, Philadelphia, USA, June 2003.

- [6] K. Yamamoto, S. Suzuki, N. Ogawa, T. Shimura, and K. Maemura, "InGaP/GaAs HBT MMICs for 5-GHz-band wireless applications-a high P1 dB, 23/4-dB step-gain low-noise amplifier and a power amplifier," in IEEE MTT-S Int'l Microwave Symp. Dig., pp. 551-554, Fort Worth, USA, June 2004.

- [7] B. Gilbert, "A new wide-band amplifier technique." IEEE J. Solid-state Circuit, Vol. SC-3, pp. 353-365, Dec. 1968.

채 규 성(Kyu-Sung Chae)

정회원

1998년 2월 경희대학교 우주 과학과 졸업 2001년 2일 건희민하고 경제

2001년 2월 경희대학교 전파 공학과 석사

2001년 3월~현재 경희대학교 전파공학과 박사과정 <관심분야> 초고주파 능동소자

모델링, RF SoC 설계, RFID/USN용 SoC 설계

김 창 우(Chang-Woo Kim) 정회원

1984년 2월 한양대학교 전자 공학과 졸업

1986년 2월 한양대학교 전자 공학과 석사

1992년 3월 일본 Shizuoka 대학원 전자 과학 연구과 공학 박사

1992년 4월~1996년 2월 (주)日本電氣(NEC) 마이 크로 렉트로닉스 연구소 연구부 주임연구원 1996년 3월~현재 경희대학교 전자정보대학 교수 <관심분야> 초고주파 능동소자 모델링, RF SoC 설계, RFID/USN용 SoC 설계