# 고밀도 비선형 광 저장장치를 위한 새로운 부분응답 최대유사도 신호 검출기 구현

준회원 이 규 석\*, 종신회원 이 재 진\*\*\*

# Implementation of a PRML Detection for Asymmetric High-density Optical Storage System

Kyusuk Lee\* Associate Member, Jaejin Lee\*\* Lifelong Member

요 약

본 논문에서는 고밀도 광기록 장치에서 발생하는 디스크 기울임 현상으로 인한 검출 성능 저하를 방지하기 위해서 디스크 기울임 분석기를 갖는 적응 등화 PRML 검출 방법을 VerilogHDL을 이용하여 구현하였다. 디스크 기울임의 분석을 위하여 고정된 패턴으로 일정한 간격마다 반복되는 동기 데이터를 이용하여 분석된 디스크의 기울임 정도를 측정하여 ROM에 저장된 등화기 계수값과 가지 메트릭의 기준값을 갱신한다. 이러한 방법은 지속적으로 계수값을 계산하여 갱신시켜줘야 하는 기존의 적응등화 방법에 비해 간단하게 각각의 계수값을 갱신시킬 수있다. Hynix 0.35㎞ STD cell library로 회로를 합성한 결과 35K 정도의 게이트를 필요로 하고 최대동작속도 140 배의 성능을 보였다.

Key Words: Optical Storage, PRML Detection, Asymmetric Optical Channel, Tangential Tilt

#### **ABSTRACT**

We implement the adaptive partial response maximum likelihood (PRML) detector with tilt analyzer for asymmetric high-density optical storage system. For the estimation of disc tilt, we exploit sync patterns in each data frame. Because of using the ROM table to renew the coefficients of equalizer and reference values of branches, the complexity of the hardware is reduced. The proposed PRML has been designed and verified by VerilogHDL and synthesized by the Synopsys Design Compiler with Hynix 0.35  $\mu$ m STD cell library. In the result, the total gate count is 35K, and the maximum operating frequency is 140 kg.

# I . 서 론

광 저장 장치의 기록 밀도가 증가함에 따라 인접 심벌간의 간섭 현상 또한 증가하게 되었다. 이로 인 해 검출 성능이 저하되는 것을 방지하기 위해서 자 기기록 저장 장치에서 사용되어오던 PRML 검출 방법이 광 저장 장치에 응용되어 왔다. 하지만, 광 저장 장치의 특성상 고정된 채널을 갖지 못하고 모 터의 진동이나 외부 충격으로 인해 디스크의 이격 현상 및 기울임 현상이 발생하여 채널의 특성이 변 화된다. 따라서, 고정된 등화기 계수값을 갖는 PRML 검출 방법으로는 검출 성능을 향상시키는데 한계를 갖게 된다.

특히 고밀도 광 기록 시스템에서 비선형적인 채널 특성을 발생시키는 가장 큰 요인은 디스크의 기울임(tangential tilt) 현상이며, 이 점을 해결하기 위

<sup>※</sup> 본 논문은 숭실대학교 연구비 지원으로 이루어졌음.

<sup>\*</sup> 삼성전자(jinrho@naver.com), \*\* 숭실대학교 정보통신전자공학부 정보저장 및 통신 연구실(zlee@ssu.ac.kr) (°: 교신저자) 논문번호: KICS2006-05-221, 접수일자: 2006년 5월 22일, 최종논문접수일자: 2006년 10월 30일

하여 여러 형태의 적응형 검출기가 제안되었다. 일 반적인 적응 등화 방식의 등화기는 비터비 검출기 의 출력 데이터를 이용하여 PR 목표(traget) 값을 계산하거나, 가지 메트릭의 기준값을 계산하는 방식 을 갖는다<sup>[1]</sup>. 하지만, 이러한 PRML 검출 방법은 몇 가지 문제점을 갖고 있다. 첫째, 등화기 계수값 을 갱신할 때, 초기에 설정한 등화기 계수값이 현재 채널 상태와 너무 차이가 많이 나면 잘못된 방향으 로 계수값이 계산되어 오히려 검출 성능을 저하시 킬 것이다. 둘째, 채널의 왜곡 현상이 심화되거나 잡음의 영향이 증가할 경우 비터비 검출기의 출력 값에 오류 발생 확률이 높아져서 잘못된 PR 목표값 을 계산하게 되고, 갱신되는 등화기의 계수값 또한 틀리게 된다. 셋째, 등화기의 탭 개수가 많을 경우, 계수값의 수렴 속도가 감소하는 문제가 발생하게 된다.

새로 제안된 검출기는 디스크가 수직으로 기울어 점에 따라 발생되는 각 채널의 특성에 맞게 모의실험을 통해 가장 적합한 등화기의 계수값과 가지 메트릭의 기준값을 계산하였다. 이렇게 계산된 계수값들은 각각의 ROM에 저장되어 채널의 상태에 따라계수값을 고속으로 갱신할 수 있도록 하였다. 이러한 디스크의 기울임(tangential tilt) 현상을 분석하기위해서 동기 데이터(synchronous data)를 이용하였다. 타이밍 회복(timing recovery)을 위해 사용되는동기 데이터는 각 프레임의 앞단에서 일정한 패턴을 갖고 주기적으로 나타나게 되는데, 이러한 데이터중 일정 구간에서 고정된 값을 갖고 반복되기 때문에 디스크 상태의 변화를 분석하기에 적합하다니.

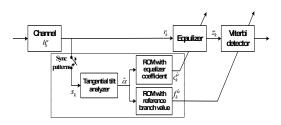

그림 1에서는 제안된 PRML 검출기의 전체 시스템 블록도를 나타내었다. 블록도 좌측의 채널을 통과하여 들어오는 데이터 가운데 동기 데이터가 발생하게 되면 스위치가 닫히게 되고, 디스크 기울임분석기(Tangential tilt analyzer)에서 디스크의 기울임각도를 분석하게 된다. 두개의 ROM에는 각각의기울임 각도에 가장 적합한 등화기 계수와 가지 메트릭(branch metric)의 기준값이 미리 계산되어 저장되어 있다. 이 값들은 앞 블록에서 분석된 기울임각도에 따라 그에 맞는 계수값 및 기준값을 동시에 갱신하게 된다.

본 논문에서는 이 검출기를 VerilogHDL을 이용하여 RTL (Register Transfer Level) 수준으로 구현하고, Synopsys Design Compiler를 이용하여 게이트 수준으로 검증하였다. II장에서는 새로운 PRML 검출기의 구현 방법에 대하여 구체적으로 기술하였

그림 1. 제안한 PRML 검출기의 전체 블록도

으며, III장을 통해 VerilogHDL 설계 및 회로합성 결과를 구하였다.

# Ⅱ. 제안된 PRML 검출기의 구현

#### 2.1. 등화기

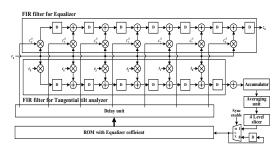

그림 2에서는 디스크 기울임 분석기를 적용한 등 화기의 구조 블록 도면을 나타내었다. 상단의 FIR 필터는 기존의 등화기에 대한 것이고, 하단의 FIR 필터는 디스크의 기울임 각도를 분석하기 위해 본 논문에서 개발한 FIR 필터이다. 채널을 통과한 데 이터  $r_k$ 는 두개의 FIR 필터를 통해 입력된다. 상단 의 FIR 필터에서는 PR(12221)에 맞게 등화된 출력 값이 비터비 디코더로 입력된다. 하단의 FIR 필터 에서는 디스크의 기울임 각도를 분석하는데, 필터 출력값은 안정된 결과값을 얻기 위해서 누산기로 보내진다. 누산기에 누적된 값은 평균기에 평균값으 로 계산되어 레벨 슬라이서로 보내지게 된다. 하지 만, 본 논문에서 개발된 적응 등화 방법은 동기 데 이터가 입력되었을 때 그 값을 이용하여 디스크의 기울임 각도를 분석하고 이에 맞는 등화기 계수값 을 갱신해야하기 때문에 싱크 데이터가 맞는 sync\_en 신호가 1이 될 때까지는 이전의 값을 유지 하도록 설계하였다. 따라서, sync\_en 신호가 1이 되 었을 때 현재 분석된 디스크의 기울임 각도가 ROM으로 전송되어 그에 맞는 계수값을 갱신하

그림 2. 디스크 기울임 각도 분석기를 갖는 등화기 구조

게 된다. 여기서 분석된 기울임 각도는 가지 메트릭의 기준값이 저장되어 있는 ROM으로 전송되어 동시에 갱신되도록 설계하였다. Delay unit은 갱신되는 계수값의 타이밍이 등화값이 계산되는 타이밍과 맞지 않기 때문에 중간에 레지스터를 삽입하여 적절한 타이밍을 맞춰주도록 설계하였다.

#### 2.2. 누산기

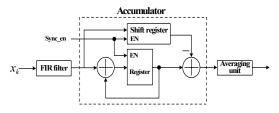

그림 3에서는 누산기의 설계도에 대한 도면을 나 타내었다. 평균값을 계산하기 위해 사용되는 누산기 를 설계함에 있어 몇 가지 문제점이 발생한다. 첫 째, FIR 필터로부터 입력되는 값을 무한히 누적할 수 없다는 점이다. 만약 무한히 누적한다면 결국에 는 계산 능력을 벗어나 오버플로우(overflow)가 발 생하게 될 것이다. 둘째로는 장시간 누적되어 수치 가 일정 값 이상이 된 후에는, 그 뒤로 입력되는 필터 출력값에 영향을 거의 받지 않아 평균값에 변 화가 없다는 문제점이 발생하게 된다. 예를 들어 1000번째까지 누적된 값이 1000이고 평균값이 1이 라고 가정했을 때, 1001번째로 들어오는 입력 값이 3이라고 한다면, 누적된 값은 1003이 되고 평균값 은 1.002라는 값이 된다. 이는 1과 거의 유사한 값 으로 다음에 입력된 필터값을 반영하지 못하고 있 다. 만약 중간에 디스크의 기울임 각도가 변하게 된 다면 변화된 각도를 찾아내지 못하게 될 것이고, 결 국에는 성능을 저하시키는 요인으로 작용하게 될 것이다. 또한, 무한히 누적된 값의 평균을 구하기 위해서는 평균기의 구조가 대단히 복잡해진다는 단 점이 있다. 따라서, 오버플로우를 방지하고 디스크 의 변화에 더욱 빠르게 적응하기 위해서 일정한 시 간 동안만 누적을 시켜 평균값을 계산하는 구조를 취하였다. 이러한 구조는 평균기의 구조를 단순화 시키는데 도움을 준다.

그림 3에서 Shift register 블록은 동기 데이터가 입력되었을 때 계산되어 들어오는 필터 출력값을 저장하는 역할을 하고, 일정 시간이 지났을 때 누적 된 값에서 빼줌으로써 정해진 시간 동안의 누적된

그림 3. 누산기의 구조

값을 유지하도록 해준다. 이에 대해서 다음과 같이 나타낼 수 있다.

$$x'_{k} = \sum_{i=k-L}^{k} x_{i}$$

(1)

현재 입력된 필터 출력값을  $x_i$ 라 하고 임의의 누적 구간을 L이라 한다. 누적된 값을 이용하여 평균기에서 평균값이 계산되고, 평균기는 L시간 동안의 누적된 값에 대해서만 적용된다. 따라서, 다음과 같은 식으로 표현할 수 있다.

$$\hat{x}_k = x'_k / L \tag{2}$$

또한,  $L=2^p$  일 경우, 평균값  $\hat{x_k}$ 는  $\hat{x_k}$ 의 2진수 값에서 앞단의 p 비트를 제외한 나머지 비트를 절삭함으로써 단순하게 계산될 수 있다. 누적값도 동기데이터가 입력되었을 때만 저장되어지도록 하기 위해서  $sync_en$  신호가 1이 되었을 때만 동작하도록설계하였다.

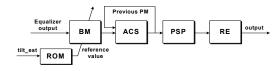

#### 2.3. 비터비 디코더

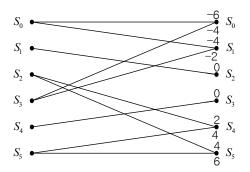

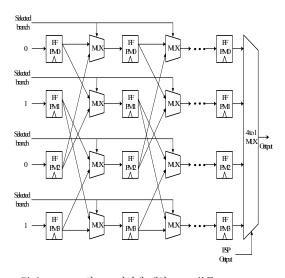

비터비 디코더의 전체 구성은 그림 4와 같이 BM (Branch Metric), ROM, ACS(Add-Compare-Select), PSP (Pick Smallest Path Metric), RE (Register Exchange)로 구성되어 있다. BM은 등화 기의 출력을 입력으로 받아, 그 입력값과 기준값과 의 오차인 Branch Metric을 계산하는 블록이다. ROM 테이블에는 미리 계산된 BM의 기준값이 저 장되어 있고, 디스크 기울임 분석기에서 들어오는 신호에 따라 기준값을 갱신시킨다. ACS는 BM값과 누적된 Path Metric(PM)값의 합을 계산하여 그 값 이 작은 PM값을 선택하고 PSP 블록으로 보낸다. 또한 트렐리스의 각 상태에 연결된 두 개의 가지 중 선택된 경로에 대한 정보를 각각 0 또는 1로 표 현하여 RE 블록에서 레지스터 교환을 하기 위한 정보로 이용된다. PSP 블록은 ACS로부터 전달받은 PM값들 중에서 가장 작은 값을 찾아 그 상태에 대 한 index를 RE 블록으로 보낸다. RE 블록은 생존 경로에 대한 정보를 순서대로 받아, 역추적 깊이만 큼 저장하면서 register exchange 알고리즘을 이용 하여 비터비 검출기의 최종 출력을 결정한다. 여기 서 BM값을 구하는 과정은 먼저 기준값들과 비터비 검출기의 입력값과의 차의 제곱값(또는 절대값)으로 BM을 계산할 수 있다. 본 논문에서는 절대값을 취 하는 방식으로 설계하였다. BM 계산에 있어서 동 작 속도를 높이기 위해, 우선 등화기의 출력에서 기 준값을 뺀 결과와 기준값에서 등화기의 출력을 뺀 결과를 구한 후, 두 가지 중 MSB의 값이 0인 결과 를 내보냄으로써 병렬처리 방식으로 절대값을 취할 수 있도록 설계하였다. 또한, 본 논문에서 사용된 17PP 코드의 특성으로 인해 발생되지 않는 코드를 생략한 결과 그림 5와 같은 가지 메트릭이 형성되 었다. 하드웨어 구성시 PM값은 시스템이 동작하는 동안 양수값(BM값)이 계속해서 누적되므로, 일정 시간이 지나면 할당된 비트로 표현할 수 있는 범위 를 넘게 된다. 이러한 문제를 해결하기 위해서는 일 정 주기마다 트렐리스 상의 각 PM값들을 조사하여 그들 중 가장 작은 값을 각각의 PM값에서 빼주어 야 하는데, 이러한 과정에서 발생하는 부하를 줄이 기 위해, Modified Modulo Normalization 방식을 적용하였다.

마지막으로 비터비 디코더의 최종 출력 방식에는 역추적(traceback) 방식과 레지스터 교환(register exchange) 방식 등이 있는데, 역추적 방식은 하드웨어 구현에 있어 레지스터 교환 방식에 비해 계산량과 사용되는 메모리의 수도 많기 때문에 효율적이지 못하므로, 동작 속도가 빠르고 구현이 용이한 레지 스터 교환 방식을 이용하였다.

RE 블록에서는 ACS 블록에서 선택 되어진 가지 정보에 따라 각 레지스터의 값을 교환하는 단계와 PSP 블록에서 결정된 최소 상태를 이용하여 최종 출력값을 결정하는 단계로 나뉘게 된다. 그림 6에서 는 이와 같은 과정을 RTL 레벨로 보여주고 있다.

# Ⅲ. 모의실험 및 회로합성 결과

제안된 PRML 검출 방법은 VerilogHDL을 이용하여 구현되었고, ModelSim5.5c를 이용하여 모의실험을 수행하였다. 모의실험을 통해 검증된 검출 방법은 Synopsys design compiler를 이용하여 게이트 수준으로 합성하였다. 목표 라이브러리는 하이닉스 0.35µm를 이용하였다. PR 목표값은 PR12221이

그림 4. 비터비 디코더의 구조

그림 5. PR(1221)의 트렐리스

그림 6. PR(121)의 RE 방식에 대한 RTL 블록도

고, 비터비 디코더의 디코딩 깊이는 30으로 설정하 였다.

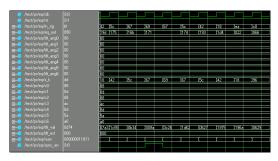

그림 7에서는 등화기의 출력값과 비터비 디코더의 출력값에 대한 모의실험 결과를 나타내고 있다. 그림 7(a)의 모의실험 결과값에서 보는 것처럼, 등화기에서는 디스크 기울임 분석기를 포함하여 채널에서 입력되는 동기 데이터를 분석하여 디스크의기울임 정도를 분석하고 판단하여 tilt\_est 라는 신호로 출력하고 있다. 이 신호 값은 두개의 ROM으로 동시에 입력되고, 등화기의 계수값 및 가지 메트릭의 기준값이 동시에 갱신된다. 또한, sync\_en 신호는 동기 데이터의 입력 상태를 나타내고 이 신호에 따라 현재 채널 상태를 분석하게 된다.

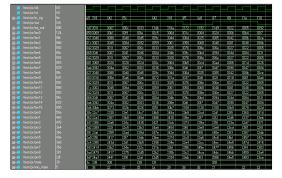

표 1에서 보는바와 같이, 이렇게 VerilogHDL을 이용한 모의실험을 통해 검증된 회로에 대해 Synopsys design compiler를 통해 게이트 수준의

(a) 디스크 기울임 분석기를 갖는 등화기

(b) 비터비 디코더

그림 7. VerilogHDL을 이용한 모의실험 결과

표 1. 모의실험 조건 및 합성 결과

| Simulator      |                     | ModelSim 5.5c                 |

|----------------|---------------------|-------------------------------|

| Synthesis tool |                     | Synopsys Design Compiler      |

| Target library |                     | Hynix 0.35μm STD cell library |

| Gate<br>count  | Equalizer           | 21K                           |

|                | Viterbi<br>detector | 14K                           |

|                | Total               | 35K                           |

| Channel Clock  |                     | 140MHz                        |

회로 합성을 수행하였다. 그 결과 총 게이트 수는 35K이었고, 디스크 기울임 분석기를 갖는 등화기는 21K, 비터비 디코더의 게이트 수는 14K를 나타내었다. 또한, 전체 클럭 속도는 140kk로써, 현재 블루레이 디스크의 1배속에 해당하는 66kk를 만족하는 속도임을 확인할 수 있었다.

# Ⅳ. 결 론

본 논문에서는 고밀도 광기록 장치에서 발생하는 디스크 기울임 현상으로 인한 검출 성능 저하를 방 지하기 위해서 디스크 기울임 분석기를 갖는 적응 등화 PRML 검출 방법을 VerilogHDL을 이용하여 구현하였고, ModelSim5.5c를 이용하여 모의실험을 수행하였다. 일정 구간마다 반복되는 동기 패턴을 LMS 알고리즘을 이용하여 구성된 FIR 필터에 의해 분석하여 현재 디스크의 기울임 정도를 판단하고, 이를 통하여 각각의 디스크 기울임에 가장 적합하게 계산되어 롬에 저장된 등화기 계수값과 가지메트릭의 기준값으로 갱신한다. 제안된 방법은 지속적으로 계수값을 계산하여 갱신시켜줘야 하는 기존의 적응등화 방법에 비해 간단하게 각각의 계수값을 갱신시킬 수 있다.

게이트 수준의 회로 합성은 Synopsys design compiler를 이용하였다. 이때, 목표 라이브러리는 하이닉스 0.35년째를 적용하였다. 그 결과 총 게이트 수는 35K이었고 전체 클럭 속도는 140版로써, 현재 블루레이 디스크의 1배속에 해당하는 66版를 만족하는 속도임을 확인할 수 있었다.

#### 참고문헌

- [1] 이규석, 이재진, "고밀도 비선형 광 저장장치를 위한 새로운 부분응답 최대유사도 신호 검출 기술," 한국통신학회논문지 2006년 10월호

- [2] Bart Van Rompaey, "The Blu-ray disc physical format," ODS 2003 Tutorial Session, Vancouver, May 2003.

- [3] Hui-Ling Lou, "Implementing the Viterbi algorithm," IEEE Signal Processing Magazine, Sep. 1995.

- [4] Khurram Muhammad, Robert B. Staszewski and Poras T. Balsara, "Speed, power, area, and latency tradeoffs in adaptive FIR filtering for PRML read channels," IEEE Trans. On VLSI Systems, vol. 9, no.1, pp. 42-51, Feb. 2001.

- [5] T. Narahara, S. Kobayashi, M. Hattori, Y. Shimpuku, G. J. Enden, J. A. H. M. Kahlman, M. Dikj and R. Woudenberg, "Optical Disc System for Digital Video Recording," *Jpn. J. Appl. Phys.*, vol. 39, no. 2B. pp. 912-919, Feb. 2000.

# 이 규 석(Kyusuk Lee)

2004년 2월 동국대학교 전자공 학과 학사

2006년 2월 동국대학교 전자공 학과 석사

2006년 2월~현재 삼성전자 연구원 <관심분야> 채널코딩, 신호검출 알고리즘, 통신시스템

# 이 재 진 (Jaejin Lee)

1983년 2월 연세대학교 전자공 학과 학사

1984년 12월 U. of Michigan, Dept. of EECS 석사

1994년 12월 Georgia Tech.Sch. of ECE 박사

1995년 1월~1995년 12월 Georg-

ia Tech. 연구원

1995년 1월~1997년 2월 현대전자 정보통신연구소 책 임연구원

1997년 3월~2005년 8월 동국대학교 전자공학과 부교수 2005년 9월~현재 숭실대학교 정보통신전자공학부 부 교수

<관심분야> 채널코딩, 스토리지 시스템, 통신이론