# SOI DTMOS 트랜지스터의 온도에 따른 hot carrier 열화현상에 관한 연구

정회원 이 재 기\*, 장 성 준\*\*, 홍 성 희\*\*

## Study on Temperature Dependence of Hot Carrier Degradation in SOI DTMOS Transistors

Jae-Ki Lee\*, Sung-Jun Jang\*\*, Sung-Hee Hong\*\* Regular Members

요 약

본 논문은 SOI DTMOS 소자의 온도에 따라 hot carrier에 의해 유발되는 소자열화 현상에 대한 연구를 수행한 것으로서, 낮은 스트레스 게이트 전압과 높은 스트레스 게이트 전압 두 가지를 인가하였다. 낮은 gate전압에서 고온으로 stress된 소자의 열화현상은 보다 높은 gate전압에서 낮은 온도로 stress된 소자의 열화보다 큼을 알 수 있었다. 그리고 DTMOS 소자와 PD MOS 소자의 온도에 따른 hot carrier영향을 비교·분석하였으며, PD MOS 소자와 비교하여 DTMOS 소자의 열화가 적은 것은 gate와 body사이의 연결에 의한 문턱전압의 감소를 초래하는 lateral electric field의 감소에 의한 것임을 알 수 있었다.

Key Words: SOI DTMOS, Hot Carrier, Degradation, Temperature, PD MOS

#### **ABSTRACT**

In this thesis, we reports the experimental results on the temperature dependence of hot carrier degradation of DTMOS devices. Both low and high stress gate voltages are used. The degradation of devices stressed at high temperature with a low gate voltage can be larger than that in devices stressed at a higher gate voltage but at a lower temperature. The temperature dependence of the hot carrier effects in DTMOS devices is compared with those in SOI PD MOSFETs. The possible mechanism explaining the less device degradation of the DTMOS, when compared to a PD MOSFET is the reduction of maximum lateral electric field resulting from the reduction of threshold voltage due to the connection between the gate and the body.

#### I . 서 론

최근에 MOS 소자의 신뢰도에 가장 중요한 영향을 미치는 요인 중의 하나가 hot carrier에 의한 소자열화 현상이다. 동작온도가 증가함에 따라 electron-phonon scattering의 mean free path가 감소하기 때문에 단채널 MOS 소자에서 hot carrier의 영향은 상온보다는 보다 높은 고온에서 덜 심각한 것

으로 사료된다.  $0.1\mu$ m 또는  $0.1\mu$ m 이하의 게이트 길이를 갖는 deep sub -micrometer MOS 소자에 대한 최근의 연구결과들은 드레인 공급 전압 보다 낮은 온도에서 충격 이온화율이 보다 작음을 보여주고 있다. N. Sano 등은  $0.1\mu$ m 이하의 소자에 있어 저온에서 충격이온화의 감소는 quasi-ballistic 이동특성과 온도에 의존적인 band-gap 에너지에 의한 것으로 실험결과를 보고하였다<sup>11</sup>. 2001년, P. Su 등

<sup>\*</sup> 가천의과학대학교 IT학과(jaekilee@gachon.ac.kr), \*\* 여주대학 컴퓨터정보과({sjjang, shhong}@yeojoo.ac.kr) 논문번호: 08030-0523, 접수일자: 2008년 5월 23일

은 self - heating 영향은 carrier heating에 영향을 끼치며, 이로 인하여 SOI 소자의 충격이온화 현상이 증가된다는 실험결과를 발표하였다<sup>12-41</sup>. S. H. Hong은 bulk 소자에 있어서, 낮은 gate 전압 stress 조건에서 hot carrier에 의해 야기되는 drain 전류의 열화현상이 stress 온도가 증가함에 따라 증가하는 것을 실험적으로 고찰하였다<sup>151</sup>. 이러한 실험결과들은 subthreshold 영역에서 drain 전류의 증가에 의해 야기되는 것임을 알 수 있다.

2001년, R. Huang 등은 bipolar - MOS mode에서 동작하는 DTMOS 소자에서 positive body bias는 floating-body partial depleted SOI 소자에서 볼수 있는 기생 bipolar transistor를 제거하기 때문에 DTMOS 소자가 partially depleted SOI 소자보다열화가 적다는 실험결과를 보고하였다<sup>[6]</sup>. 하지만 SOI DTMOS소자의 온도에 따른 hot carrier 열화현상에 대한 연구결과는 아직까지 보고되지 않고있다<sup>7]</sup>.

#### Ⅱ. 연구방법

논문에서는 SIMOX 기판위에 partially depleted **DTMOS** 구조를 사용하였으며, enhancement mode n-channel MOS소자를 standard SOI CMOS 공정을 사용하여 제작하였다. buried oxide 두께는 400nm, gate oxide 두께는 8nm이며, 두께는 80nm이다. body는 Al interconnect를 통하여 gate에 연결하였다. channel doping 농도는 대략  $9 \times 10^{16} \text{cm}^{-3}$  정도 이다. 또한 DTMOS소자와 동일한 구조와 기술적인 parameter 들을 사용하여 PDMOS소자를 동일한 chip에 제작 하였다. channel 길이와 두께는 각각 0.3 μm와 10 μm 이다. Hot carrier stress를 위하여 여러 gate biases 에서 temperature-regulated hot chuck을 사용하여 수행하였으며, stress 온도는 25℃에서 125℃까지 수행하였다.

#### Ⅲ. 연구결과 및 고찰

#### 3.1 고온에서 소자열화 현상의 증가

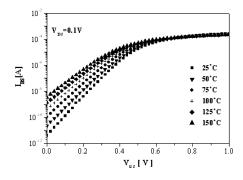

그림 1은 온도에 따른 DTMOS 소자의 drain 전류와 gate 전압 특성을 보여주고 있다. 낮은 gate전압 영역에서는 drain 전류가 온도에 따라 증가하나 높은 gate전압 영역에서는 감소하는 것을 알 수 있다. zero-temperature coefficient(ZTC) gate 전압은

drain 전류가 온도에 영향을 받지 않는 gate전압으로 정의되어 진다. 그림 1로부터 ZTC가 0.7V임을 알 수 있다. ZTC point 이하에서 온도에 따른 drain 전류의 증가는 subthreshold 영역에서 확산전류의 증가에 의한 것이며, ZTC point 이상에서 온도에 따른 drain전류의 감소는 표면 이동도의 감소에 의한 것이다.

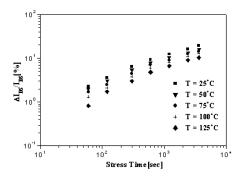

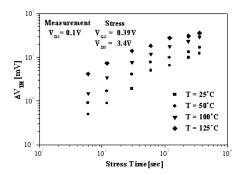

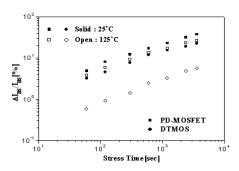

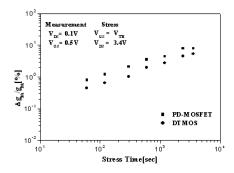

그림 2는 saturation 영역에서 hot-carrier에 의한 drain전류의 열화현상을 여러 온도에서 stress 시간 의 함수로서 보여주고 있다. drain stress 전압은 3.4V이며, gate전압은 그림 2(a)는 0.7V, 그림 2(b) 는 0.39V이다. Drain과 gate의 측정 전압은 0.7V이 다.  $V_{GS} = 0.7$ V일 때 온도가 증가함에 따라 drain 전 류의 열화가 감소하나,  $V_{GS}=0.39$ V일 때는 온도가 증가함에 따라 drain 전류의 열화가 증가한다. 소자 의 열화현상은 maximum lateral electric field( $E_m$ ) 에 의한 drain 전류에 비례함을 잘 알고 있다.  $V_{GS}$  = 0.39V일 때, 소자열화의 증가는 온도의 증가에 따 른 drain 전류의 증가에 의한 것이다. 비록  $E_m$ 이 문턱전압의 감소로 초래되는 drain 포화전압의 증가 에 의하여 고온에서 감소하나, drain 전류의 증가는 고온에서 소자의 열화를 증가시키는 매우 중요한 요소라고 생각할 수 있다.

온도에 종속적인 drain 전류의 열화를 반전시킬 수 있는 cross-over stress gate 전압은 정확하게 ZTC gate 전압과 일치하지는 않는다<sup>17</sup>.

본 논문에서는 cross-over 전압이 ZTC point보다 낮음을 관찰할 수 있었다. cross-over 전압과 ZTC point의 차이는 drain 전류의 열화가 drain 전류와  $E_m$  에 비례한다는 것임을 알 수 있다. 비록 drain 전류가 cross-over 전압과 ZTC 사이의 범위에서 온도에 따라 약간 증가를 하더라도, 온도에 따른 문턱 전압의 감소는  $E_m$ 의 감소를 초래하는 drain 포화전압의 증가를 유발하며, 이에 대한 순수한 소자열화의 감소현상을 고찰할 수 있었다.

또한, 그림 2에서 온도에 따른 drain 전류 열화의 변화는 stress 시간의 증가에 따라 크게 중요하지는 않지만, 열화율 n은 power time dependence  $law(\Delta I_{DS}/I_{DS}=t^n)$ 로부터 추출할 수 있다. 그림 2(a)로부터,  $V_{GS}$ =0.7V일 때 n은 모든 stress 온도 동안에 약 0.5이다. 그림 2(b)로부터,  $V_{GS}$ =0.39V일 때 n은 25 $^{\circ}$ C에서 0.5이나, stress 온도가 증가함에 따라 n은 감소한다. SOI MOS 소자의 경우에 일

그림 1. 온도에 따른 DTMOS 소자의 drain 전류와 gate 전 압 특성

그림 2. (a)  $V_{\rm GS}=0.7V$  일 때 여러 온도에서 stress 시간에 따른 hot-carrier에 의한 drain전류 열화

그림 2. (b)  $V_{GS}=0.39V$  일 때 여러 온도에서 stress 시간에 따른 hot-carrier에 의한 drain전류 열화

반적으로 electron이나 hole 둘 중에 하나만 주입되는 동안에는 n이 약 0.25정도이나 electron과 hole 모두 주입되는 동안에는 n이 약 0.5정도로 알려져 있다 $^{8-9}$ . 따라서 stress 온도에 따른 n의 감소는 보다 높은 stress 온도에서 hole 주입과 관련하여 electron 주입이 증가함을 의미한다.

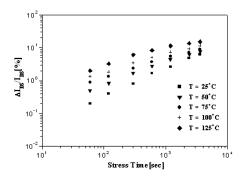

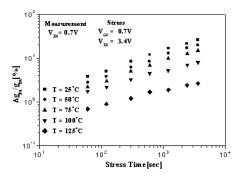

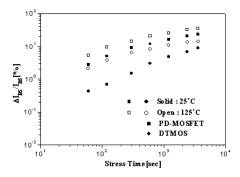

그림 3은 여러 온도에서 stress 시간에 따른

그림. 3. (a)  $V_{\rm GS}=0.7V$  일 때 여러 온도에서 stress 시간에 따른 hot-carrier에 의한 문턱전압 변화

그림 3. (b)  $V_{GS}=0.39V$  일 때 여러 온도에서 stress 시간에 따른 hot-carrier에 의한 문턱전압 변화

hot-carrier에 의한 문턱전압의 변화를 보여주고 있다. drain stress 전압은 3.4V이며, gate전압은 그 림 3(a)는 0.7V, 그림 3(b)는 0.39V이다. drain 측 정 전압은 0.1V이다. 또한 그림 3에서  $V_{GS}=0.7$ V일 때 온도가 증가하면 문턱전압의 변화가 감소함을 알 수 있으나,  $V_{GS} = 0.39$ V일 때는 온도가 증가하면 문턱전압의 변화 역시 증가되는 것을 알 수 있다. stress 후의 문턱전압의 양(+)의 값으로의 변화는 주 로 gate oxide의 volume까지 electron 주입에 의하 여 초래된다. 그리고 문턱전압의 변화가 25℃에서  $V_{GS} = 0.39$ V일 때보다  $V_{GS} = 0.7$ V일 때 더욱 심각함 을 알 수 있었다. 또한 그림 3은 비록 gate stress 전압이 낮을 지라도 고온에서 stress된 소자의 문턱 전압 변화가 보다 심각함을 보여주고 있다. transconductance의 열화는 주로 Coulomb scattering 을 유발하는 Si-SiO<sub>2</sub> 경계면에서 생성된 결함과 연 관하여 주목해야할 가치가 있다.

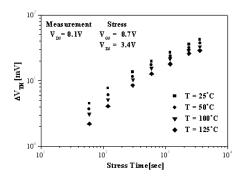

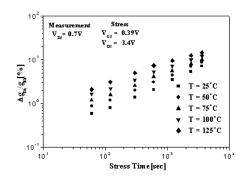

그림 4는 여러 온도에서 stress 시간에 따른

hot-carrier에 의한 transconductance 열화현상을 보여주고 있다. drain stress 전압은 3.4V이며, gate전압은 그림 4(a)는 0.7V, 그림 4(b)는 0.39V이다. drain 측정 전압은 0.7V이다. 그림 3에서 보는 바와같이  $V_{GS} = 0.7$ V일 때 온도가 증가하면 transconductance의 열화는 감소하나,  $V_{GS} = 0.39$ V일 때는 온도가 증가하면 transcond- uctance의 열화가 증가한다.  $V_{GS} = 0.39$ V일 때 transconductance의 열화가 증가한 것은 고온 stress에서 보다 많은 interface states가 생성되기 때문이다.

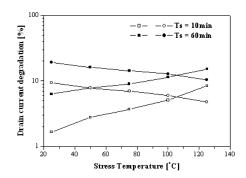

그림 5는 여러 stress gate 전압 조건에서 stress 온도에 따른 drain전류의 열화현상을 보여주고 있다.  $V_{GS}=0.7$ V에서 stress된 소자의 drain전류 열화는 stress 온도에 따라 감소하나  $V_{GS}=0.39$ V에서 stress된 소자의 drain전류 열화는 stress 온도에 따라 증가함을 알 수 있다. 100  $\mathbb C$ 이하의 stress 온도에서 drain 전류 열화율 $(\Delta I_{DS}/I_{DS})$ 의 절대값의 변화가  $V_{GS}=0.39$ V일 때 보다는  $V_{GS}=0.7$ V일 때 더욱 커집을 알 수 있다.

그림 4. (a)  $V_{GS}=0.7V$  일 때 여러 온도에서 stress 시간에 따른 hot-carrier에 의한 trans- conductance 열화

그림 4. (b)  $V_{GS}=0.39V$  일 때 여러 온도에서 stress 시간에 따른 hot-carrier에 의한 trans- conductance 열화

그림 5. 여러 strss gate 전압 조건에서 stress 온도에 따른 drain전류 열화

그러나 110 인이상의 stress 온도에서는  $V_{GS}$  = 0.39V에서 stress된 소자의 drain전류 열화가  $V_{GS}$  = 0.7V에서 stress된 소자의 drain전류 열화보다 더 커짐을 알 수 있다. 이러한 결과는 비록 stress gate 전압이 낮을 지라도 고온에서 stress된 소자의 drain 전류 열화가 매우 심각함을 보여준다.

#### 3.2 DTMOS와 PDMOS 소자의 열화현상

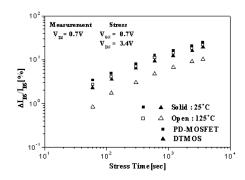

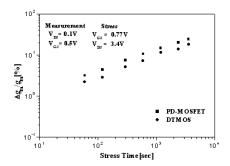

그림 6은 stress 시간에 따른 DTMOS와 PDMOS의 drain전류 열화현상을 보여주고 있다. drain stress 전압은 3.4V이며, stress gate전압은 그림 6(a)는 0.7V이며, 그림 6(b)는 PDMOS와 DTMOS 소자에  $V_{GS} = V_{TH}$  (각각 0.53V와 0.39V)인 조건으로 stress를 인가하였다. drain전류의 열화는 drain 전류와  $E_m$  모두에 비례하기 때문에,  $V_{GS} = V_{TH}$ 로 stress를 인가하였을 때 PDMOS와 DTMOS 소자 둘 다 동일한 drain전류를 갖는다. 온도에 따른 소자열화 현상을 비교하기 위하여 두 소자를 25  $^{\circ}$ 은 와 125  $^{\circ}$ 은에서 stress를 인가하였으며, DTMOS 소자의 drain전류의 열화가 PDMOS 소자의 열화보다 적음을 알수 있었다.

그림 6(a)는  $V_{GS}=0.7V$ 일 때 온도가 증가함에 따라 PDMOS와 DTMOS 소자의 drain전류의 열화가 감소하는 것을 보여주고 있다. 그러나  $V_{GS}=V_{TH}$ 인 조건에서는 반대로 결과가 나타나는 것을 그림 6-b에서 보여주고 있다. 그림 6(a)와 그림 6(b)로부터  $V_{GS}=0.39V$ 이고 125  $^{\circ}$ C에서 1000초 동안 stress를 인가한 DTMOS의 열화가  $V_{GS}=0.7V$ 이고 25  $^{\circ}$ C에서 1000초 동안 stress를 인가한 PDMOS의 열화보다 더 큰 것을 알 수 있다. 이러한 결과는 낮은 gate전 압으로 stress를 인가한 DTMOS 소자가 고온 stress

그림 6. (a)  $V_{GS}=0.7V$  일 때 stress 시간에 따른 DTMOS 와 PDMOS의 drain전류 열화

그림 6. (b)  $V_{GS} = V_{TH}$  일 때 stress 시간에 따른 DTMOS 와 PDMOS의 drain전류 열화

를 충분히 인가하고 보다 큰 gate전압으로 stress를 가한 PDMOS 소자에서 관찰할 수 있는 것 보다 더 큰 열화를 유발시킨다는 것을 의미한다. 그림 6-b에서, DTMOS 소자에 각각 25℃와 125℃로 stress를 인가했을 때 drain전류 열화의 차이는 PDMOS 소자의 차이보다 더 크다. 이러한 이유는 온도에 따라 drain전류의 증가가 DTMOS 소자에서 더 크기 때문이다. gate stress 전압이 낮을 때, DTMOS의 stress 온도에 따른 소자열화에 대한 민 감성이 PDMOS 소자보다 더 크다는 것에 주목해야 한다

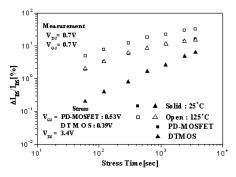

그림 7은 포화영역에서 stress 시간에 따른 DTMOS 소자와 PDMOS 소자의 drain전류 열화를 보여주고 있다. drain stress 전압은 3.4V이며, stress gate전압은 그림 7(a)는 0.7V이며, 그림 7(b)는 PDMOS와 DTMOS 소자에  $V_{GS} = V_{TH}$  (각각0.53V와 0.39V)인 조건으로 stress를 인가하였다. gate전압과 온도를 stressing하는 동안에 DTMOS 소자의 drain전류열화가 PDMOS 소자보다 적음을 알 수

그림 7. (a)  $V_{GS}=0.7V$  일 때 포화영역에서 stress 시간에 따른 DTMOS와 PDMOS의 drain전류 열화

그림 7. (b)  $V_{GS}=V_{TH}$  일 때 포화영역에서 stress 시간에 따른 DTMOS와 PDMOS의 drain전류 열화

있다. 이러한 결과는 DTMOS 소자에 문턱전압의 감소를 초래하는  $E_m$ 의 감소와 body의 positive biasing에 의한 drain 포화전압의 증가로 설명되어 질 수 있다.

일반적으로 transconductance의 열화는 Si- SiO<sub>2</sub> 경계면에서 interface states의 생성에 의한 것으로 알려져 있다. 그림 8은 선형영역에서 stress 시간에 따른 DTMOS와 PDMOS소자의 transconductance 열화를 보여주고 있다

Drain stress 전압은 모든 소자에 3.4V를 인가하였다. 일부 PDMOS 소자와 DTMOS 소자는  $V_{GS} = V_{TH}$  인 조건으로 stress를 인가하였으며, 나머지 소자들은  $V_{GS} = 0.7$ V인 조건으로 stress를 인가하였다. 그림 8로부터 모든 stress 조건하에서 PDMOS 소자의 transconductance 열화가 DTMOS소자보다 더욱 심각함을 알 수 있다.

이러한 이유는 hot carrier stress 후에 PDMOS 소자에서 더욱 더 많은 interface states를 생성하기 때문이다.

그림 8. (a)  $V_{GS}=V_{TH}$  일 때 선형영역에서 stress 시간에 따른 DTMOS와 PDMOS의 transconductance 열화

그림 8. (b)  $V_{\rm GS}=0.7V$  일 때 선형영역에서 stress 시간에 따른 DTMOS와 PDMOS의 transconductance 열화

### Ⅳ. 결 론

본 논문은 DTMOS 소자의 온도에 따른 hot carrier 열화현상을 실험적으로 연구하였다. 낮은 gate전압에서 stress 온도가 증가함에 따라 소자의 열화가 증가함을 알 수 있었다. 낮은 gate전압에서 고온으로 stress된 소자의 열화현상은 보다 높은 gate전압에서낮은 온도로 stress된 소자의 열화보다 큼을 알 수 있었다. PD MOS 소자와 비교하여 DTMOS 소자의 열화가 적은 것은 gate와 body사이의 연결에 의한 문턱전압의 감소를 초래하는 lateral electric field의 감소에 의한 것임을 알 수 있었다.

#### 참 고 문 헌

[1] A. Raychaudhuri, M. J. Deen, W. S. Kwan, and M. I. H. King, "Features and mechanisms of the saturating hot-carrier degradation in LDD NMOSFET's," IEEE Trans. Electron Devices. vol.43, pp.1114-1122, 1996.

- [2] p.Su, K. Goto, T. Sugii, and C. Hu, "Self-heating enhanced impact ionization in SOI MOSFETs," in Proc. IEEE Int. SOI Conf., pp.31-32. 2001.

- [3] p.G. Mautry, and J. Trager, "Investigation of self-heating in VLSI and ULSI MOSFET's" in Proc. IEEE Conf., Microelectron. Test structures, pp.221-226, 1990.

- [4] A. Caviglia, and A. A. Ilidais, "A new method for characterizing dynamic self-heating in SOI MOSFET's," in Proc. IEEE Int. SOI Conf., pp.118-119, 1992.

- [5] S. H. Hong "Impact of hot carriers on DRAM circuits at elevated temperature," Ph. D. dissertation, Univ.of Incheon, 2002.

- [6] R. Huang, J. Wang, X. Zhang, and Y. Wang, "Hot Carrier Induced Degradation in Mesa-Isolated n-Channel SOI MOSFETS Operating in a Bi-MOS mode," IEEE Trans. Electron Devices, vol.48, no.8, pp.1594-1598, 2001.

- [7] J. K. Lee, N. J. Choi, C. G. Yu, J. p.Colinge, and J. T. Park, "Temperature dependence of hot carrier degradation in SOI DTMOS transistors," IEEE Electron Device Lett. vol.23, no.11, pp.673-675, 2002.

- [8] S. p.Sinha, F. L. Duan, and D. E. Ioannou, "Time dependence power law of hot carrier degradation in SOI MOSFET's," in Proc. IEEE Int. SOI Conf., pp.18-19, 1996.

- [9] Keith A. Jenkins, J. Y.-C. Sun, and J. Gautier, "Characteristics of SOI FET's under pulsed conditions," IEEE Trans. Electron Device vol.44, no.11, pp.1923-1930, 1997.

이 재 기(Jae-Ki Lee)

정회원

한국통신학회 논문지 제32권 제12호 참조

장 성 준 (Sung-Jun Jang)

정회원

한국통신학회 논문지 제28권 10T호 참조

홍 성 희 (Sung-Hee Hong)정회원한국통신학회 논문지 제32권 제12호참조