# 모바일 멀티미디어 응용을 위한 고에너지효율 재구성형 프로세서의 설계 및 제작

정회원 여 순 일\*. 이 재 흥\*\*

# Design and Fabrication of High Energy Efficient Reconfigurable Processor for Mobile Multimedia Applications

Soon-il Yeo\*, Jae-Heung Lee\*\* Regular Members

요 약

모바일 멀티미디어 응용을 위한 기존의 프로세서들이 다방면에서 검증되고 응용되고 있다. 그런데, 이 모바일 멀티미디어 응용을 위해서 채택할 수 있는 하드 와이어드 즉 ASIC으로 된 칩 솔루션은 유연성이 떨어지며 비용이 많이 소요된다. 또한 유연성이 큰 CPU 솔루션은 그 성능에서 한계에 봉착하게 된다. 그러므로 ASIC 과 같은 성능과 CPU 같은 유연성 모두를 충족시키는 방법으로 재구성형 연산 프로세서를 사용하는 방법이 추천된다. 특히, 모바일 시스템들은 저전력과 고성능을 같이 추구하고 있으므로 본 논문에서는 이들을 모두 충족시키는 고에 너지효율을 가지는 재구성형 프로세서를 제안한다. 130nm CMOS 기술에 의해 제작된 것은 121MOPS/mW의에너지효율을 보이며 이를 90nm CMOS 기술과 명령어의 효율적인 사용을 통한 재구성형 프로세서의 시뮬레이션 결과는 539MOPS/mW의 에너지효율을 보임을 확인하였다. 또한 그 응용을 MP3의 IMDCT와 MPEG4의 DF H.264의 ME 알고리즘에 대해 시행함으로써 모바일 멀티미디어 분야에 적용될 수 있음을 보였다.

Key Words: Reconfigurable processor, Energy efficiency, Flexibility, Mobile multimedia

# **ABSTRACT**

Applications for mobile multimedia are testing the performance limits of present day CPUs with variety. However, hardwired solutions are inflexible and expensive to develop. CPUs with flexibity have limitation of performance. So, the requirement for both ASIC-like performance and CPU-like flexibility has led to reconfigurable processor. Mobile systems require low power and high performance concurrently. In this paper, we propose reconfigurable processor for mobile multimedia with high energy efficiency. Reconfigurable processor with 121MOPS/mW is developed by 130nm CMOS technology. And the processor was simulated for energy efficiency with 539MOPS/mW by 90nm CMOS technology and effective use of instructions. And we tested its applications for multimedia field. We tested the case of inverse MDCT for MP3 and DF for MPEG4 and ME for H.264.

I. 서 론

가 과거에 비해 비약적인 증가를 가져 오게 되었는데 그 이유는 칩에서 처리해야 할 데이터의 양이 대폭 증가하면서 임베디드 메모리가 증가하게 되고

근래에 들어 SoC(System On a Chip)의 집적도

<sup>※</sup> 본 논문은 정보통신부 및 정보통신연구진흥원의 IT신성장동력핵심기술개발사업의 부분지원으로 수행하였습니다.[2006-S-006-01, 유 비쿼터스 단말용 부품/모듈]

<sup>\*</sup> 한국전자통신연구원 융합부품.소재연구부문 NT융합부품연구부(siyeo@etri.re.kr) \*\*국립한밭대학교 컴퓨터공학과 논문번호: KICS2008-05-213, 접수일자: 2008년 5월 14일, 최종논문접수일자: 2008년 11월 5일

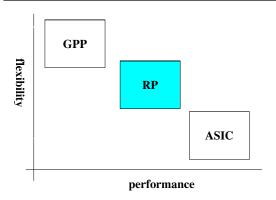

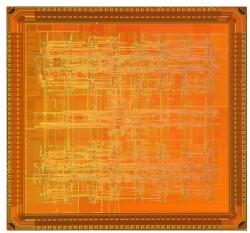

그림 1. 스트림데이터 처리방법 상호비교

시스템복잡도의 증가에 따라 칩의 집적도가 뒷받침 이 되어야 칩으로 제작이 가능해 지는 등의 이유를 들 수 있다. 특히 멀티미디어 SoC의 경우에는 대용 량 데이터 처리에 대한 요구가 있어 더욱 그러하다. 스트림 형태의 데이터로 인해 단일 프로세서로는 데이터 처리가 불가능해 지는 단계에 까지 이르게 되었다. 따라서 이러한 스트림 데이터를 처리하기 위한 여러 가지 시도가 있어 왔다. 이들을 그림1에 나타내었는데 첫째로 GPP(General Purpose Processor)를 사용하는 것인데 유연성(flexibility)은 뛰어나나 연산성능(performance)이 미치지 못하는 문제점이 있다. 둘째로는 하드와이어드 ASIC을 사 용하는 방법인데 고성능 동작이 가능하나 국한된 기능만을 수행하게 되는 문제점이 있다. 세 번째로 재구성형 프로세서(RP: Reconfigurable Processor)를 사용하여 GPP와 ASIC의 단점을 보완 하고자 하는 시도이다. 즉 RP는 GPP보다 고성능이 나 유연성이 떨어지고 ASIC보다는 유연성이 뛰어 나나 성능이 떨어지는 점이 있다. RP는 대용량 스 트립데이터를

처리하는 하나의 유력한 방법이므로 많은 연구자들에 의해서 다루어져 온 분야이다.[1]-[8] 본 논문에서는 특히 모바일 멀티미디어 분야에 응용할 수 있는 RP에 대해서 다룬다. 즉, 오디오와 비디오에 대한 응용을 보인다. 한편, 모바일 응용을 위해서는 저 전력, 고성 능을 동시에 만족해야 하므로 우선 이를 만족하는 재구성형 프로세서를 고려한다. 그러므로 전력과 성능을 동시에 표현하는 에너지효율에 대한 정의를 한 후이에 따른 고에너지효율 재구성형 프로세서를 개발한다. 이를 MP3의 Inverse MDCT알고리즘과 MPEG4의 다블록킹 필터 알고리즘, H.264의 ME(Motion-Estimation)블록에 적용함으로써 재구성 응용 분야에 대해서도 적합한 것임을 보인다.

## Ⅱ. 에너지 효율

모바일 시스템에서의 저 전력에 대한 요구는 필수적이라 할 수 있다. 아울러 고성능까지 구비되어야 할 것이다. 그러므로 모바일 시스템이나 모바일용 SoC에서는 고에너지효율 특성을 가지는 것이 요구된다 하겠다. 위의 저 전력이나 고성능에 대해서는 전통적인 측정방법과 측정단위가 있으므로 이들을 조합한 에너지 효율(Eeff)에 대한 식을 아래와같이 세울 수 있다.

성능(Performance(H))은 모바일용 SoC의 데이터 처 리능력으로 정의할 수 있는 것인데 이것은 클록의 속도로 표현할 수 있다. 즉, H는 재구성형 SoC가 포함된 모바일 시스템에서 실제 시스템의 성능을 표현할 수 있는 측정요소로 작용한다. 전력(P)은 동 작하는 SoC의 전력을 의미하는데 모바일 시스템 및 SoC에서의 전력요소는 매우 중요한 요소로써 작용 되는 것이다. 모바일 시스템에서는 전력과 성능 이 양자가 주요 요소로 측정될 수 있는 에너지효율 (Eeff)개념을 도입하도록 본 논문에서는 제안한다. 프로세서 영역에서 H는 OPS(Operation Per Second)로 표현되며 P는 W(Watt)로 나타낸다. 요 즈음, H는 MOPS(Mega Operations Per Second) 수준 혹은 GOPS(Giga Operations Per Second)로 나타나고 P는 수 W 나 수백 mW로 나타난다. STARC (Semicon- ductor Technology Academic Research Center)로드맵에 의하면 130nm 기술에서 10GOPS, 100mW(즉 100MOPS/mW) 90nm 기술에 서 30GOPS, 100mW(즉 300MOPS/mW)로 예측하 고 있다.[www.starc.jp]

#### Ⅲ. 재구성형 프로세서

# 3.1 재구성 구조

재구성 구조를 최초로 제안한 사람은 G.Estrin 이다.[1] 그림 1에서 보는 바와 같이 재구성 구조는ASIC (Application Specific Integrated Circuits)에 비해서 유연성에 장점이 있다. 재구성 구조는 비트 단위로 구 성되는 파인 그레인 구조(Fine Grain Architecture)와 워드 단위로 구성되는 코어스 그레인 구조(Coarse Grain Architecture)가 있으며 재구성 단위의 결합관계 에 따라 Loosely-coupled, Bus-coupled, Tightly-coupled

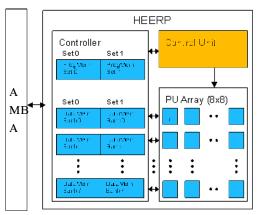

그림 2. HEERP의 구조도

재구성 단위로 나눌 수 있는데 이것은 재구성 단위가 프로세싱 유닛에 대한 위치로 구별되게 된다. [2][3][4] 한 편, 본논문에서 다루는 고에너지효율을 지향하는 구조는 새롭게 시도되는 것이다. [5][6][7]

#### 3.2 HEERP의 개발

모바일 멀티미디어에 응용하기 위한 재구성형 프로 세서인 HEERP(High Energy Efficiency Reconfigurable Processor)를 개발하였는데 이는 크게 3가지 블록으로 구성이 된다. HEERP는 그림 2에서 보이는 바와 같이 Controller, Control Unit, 8x8PU(Processing Unit) Array부로 나뉘어진다.(그림2에서는 HEERP가 AMBA에 연결되어 있음을 보인다).

#### IV. HEERP의 설계, 제작 및 칩 테스트

#### 4.1 HEERP의 설계 및 제작

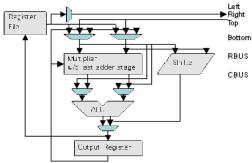

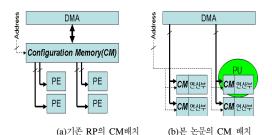

HEERP는 그림 2와 그림 3에 보이는 구조를 근거 로 설계하였는데 여기서는 고에너지효율을 가지는 HEERP를 구현하기 위한 제안을 설명하다. Configuration Me- mory(CM)를 그림 3의 연산부와 인접 배치하고(그림4(b)) 이를 그림 3의 CBUS와 연 결되게 하여 이들을 하나의 PU로 구성되게 한다. 이 것은 유사한 Array구조를 가지는 재구성형 프로세서 들이 채택하고 있는([5][8][9]) Configuration Memory 의 배치(그림4의 (a))방법과 다른 것으로 시뮬레이션 결과 최대 약 2ns 정도의 Clock Period 향상을 가져왔 다. 또한, 인터커넥션(연결선)의 숫자도 그림4의 (a)경 우보다 (b)가 대폭 감소하게 되는데 (a)의 경우 PE(Processing Element)마다 연결선이 필요하게 되어 8x8 Array로 한다면 64개의 PE를 각각 연결해야 되 는 반면 (b)에서는 8개의 PU를 한 그룹으로 묶어 처

그림 3. 간략화된 연산부 구조

(a)기존 RP의 CM배치 (b)본 논문의 CP 그림 4. Configuration Memory(CM)의 배치 방법

리하는 방법을 사용함으로써 연결선 개수가 8배 줄어 들게 되어 칩 면적의 감소와 더불어 전력도 줄일 수 있다. 또한, PU간의 연결을 위해 참조하는 PU를 인접 한 것들에게만 연결이 되게 하는 구조(그림3의 Left, Right, Top, Bottom의 버스라인-인접 PU의 위치에 따 른)를 채택함으로써 RP 전체적인 연결선의 숫자가 추 가로 감소되는 효과가 있다. 이렇게 하면 해당 명령어 가 1 Cycle 내에 인접 PU들을 참조하여 처리 되므로 성능 향상도 기할 수 있게 된다. 한편, 그림3과 같이 연산부의 구조를 간략화 하도록 하였는데 여기서는 MAC(Multiply and Accumulation)연산에 필요한 추가 Adder를 사용하지 않음을 볼 수 있다. 이렇게 함으로 써 MAC이 차지할 수 있는 면적과 전력을 줄이도록 하였다. 이것은 동영상 처리에 MAC연산은 그 빈도가 적으므로 위와 같이 추가 Adder를 없애도록 한 것이 다. 또한, 그림2에 보이는 대로 HEERP 구조는 Controller부에 프로그램 메모리와 데이터 메모리를 각각 2세트를 배치함으로써 Set1을 통하여 즉시 처리 될 내용이 저장되게 되고, Set0를 통하여 그 다음에 처리될 내용이 저장되게 되도록 함으로써(2Set 구조 제안) 처리시간을 신속하게 하도록 도모하였다. 본 논 문에서 제안하는 또 다른 것은 SIMD/MIMD 병용 방 식이다. 표 5에서 보면 유사한 다른 재구성형 프로세 서들은 SIMD나 MIMD 중 하나의 방식만 채택하고 있는 것을 볼 수 있는데 본 논문의 재구성형 프로세서

는 SIMD/MIMD 병용으로 사용할 수 있도록 되어 있 어 연산방식 선택에 따라 효율적인 연산을 기할 수 있 다. 아울러, HEERP의 동작에 관련된 설명을 하면, 그 림3의 연산부에 RBUS를 통하여 비트 스트림 데이터 가 들어오며, CBUS를 통하여 이들에 대한 명령어(PU Instruction)가 들어오게 되는데 명령어는 미리 인접 메모리 블록(Configuration memory)에 저장하는 방법 을 사용하여 재구성 동작이 이루어지도록 한다. 그 동작을 위해 External Command와 PU Instruction을 정 의하였고 표 1, 그림 5에서 보인다. 그림 2의 프로그 램메모리(Progmem)와 데이터메모리(Datamem)는 AMBA와 연결되어 AMBA의 데이터를 받아들이도록 되어 있다. 이렇게 받아들여진 데이터들은 그림2의 Control Unit으로 보내져서 PU Array(8x8)에 전달되 게 되는데 프로그램은 그림3의 CBUS를 통하여 연산 부에 전달이 되게 되고 데이터는 그림3의 RBUS를 통 해 연산부에 전달된 후 재구성 연산동작을 하게 된다. 여기에서 처리되는 Data는 주로 Stream Data인데 이 를 Bit Stream으로 만드는 역할은 ARM프로세서를 통해 하도록 하고 있다. 또한 여기서 저 전력 설계를 위해 Configuration Memory는 16개의 명령어가 처리 되는 것을 최대 크기로 한 설계를 하였다(그림5). 그 것은 모바일 멀티미디어 처리를 위한 최소한의 명령 어 세트 구조를 설계한 결과이다. 한편, PU의 합성설

표 1. HEERP의 External Command

| Command   | Description                          |  |  |

|-----------|--------------------------------------|--|--|

| CFGSET    | Set Config. Data to Config. Memory   |  |  |

| PROGSET   | Set Program to Program Memory        |  |  |

| PROGEXEC  | Execute Program                      |  |  |

| PROGSTATE | Retrieve Process State               |  |  |

| DMSET     | Set Operand Data to Data Memory      |  |  |

| DMGET     | Retrieve Data from Data Memory       |  |  |

| DMSET8    | Set 8bit Operand Data to Data Memory |  |  |

| DMGET8    | Retrieve 8 bit Data from Data Memory |  |  |

(a) Binary format of PU instructions

NOOP/RST

MOVI[ACC]imValue[>Dest] [, ExtReg [>RO |>CO |>RO, CO]]

ADD[CND]SrcA, SrcB[>Dest] [, ExtReg [>RO |>CO |>RO, CO]]

SUB/AND/OR/XOR/NOT/MUL/MUX/MIN/MID/SLL/SRL/SRA

(b) Instructions of PU

그림 5. PU의 Instruction Set Architecture

표 2. HEERP의 합성설계 결과

| Technology        | TSMC 130nm LV CMOS |  |  |

|-------------------|--------------------|--|--|

| Synthesis Tool    | DC Ultra           |  |  |

| Clock Period      | 6ns analysis       |  |  |

| Total Cell Area   | 30,378,296 unit    |  |  |

| Operation Mode    | SIMD/MIMD          |  |  |

| Total Power       | 169mW              |  |  |

| Energy Efficiency | 126MOPS/mW         |  |  |

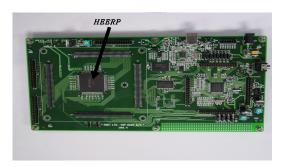

계에 있어 Critical Path 최소화 설계를 하여 에너지효 율이 향상되도록 하였다. 표 2에 HEERP의 Verilog를 사용한 합성설계결과를 보이는데 0.13년때공정기술을 적용하여 그 에너지효율이 126MOPS/mW가 됨을 알 수 있다. 이렇게 함으로써 고성능과 저전력 특성을 가지는 병렬 프로세서를 지향할 수 있게 되었다. 즉, 130nm 즉 0.13@ 기술로 100MOPS/mW급에 해당하 는 재구성형 프로세서가 설계되었고 이를 모바일 멀 티미 디어분야에 적용할 수 있도록 그 터전을 마련하 였다. 위와 같이 설계한 후 실제적으로 칩을 제작하였 는데 TSMC의 저전력 공정라이브러리를 사용하였다. 제작된 칩 사이즈는 5mm x 5mm인데 이는 TSMC셔 틀을 이용하였기 때문이다. 시뮬레이션 결과 칩 사이 즈는 PAD를 제외하고 3.4mm x 3.2mm로 되었다 (Teraform 시뮬레이션 결과). 패키지는 144 pin QFP 가 사용되었고 그림 6에 제작된 HEERP의 칩 사진을 보였다.

#### 4.2 HEERP의 테스트

HEERP의 칩 테스트를 위해 Quartet장비를 사용하였는데 최대 측정 범위가 100MHz(10ns Clock)까지이므로 6ns Clock(166MHz) 측정은 이루어 지지 못하였다. 아래 표 3은 100MHz(즉 10ns) 측정 결과이며 전력은 평균전력을 측정할 수 있는 테스트 벡터를 별도로 생성하여 Quartet에서 측정한 결과이

표 3. HEERP의 칩 테스트 결과

| Technology              | TSMC 130nm LV CMOS        |  |  |

|-------------------------|---------------------------|--|--|

| Test Apparatus          | Quartet (made by Quartet) |  |  |

| operation voltage(core) | 945mV~1.4V                |  |  |

| operation voltage(I/O)  | 1.8V~3.4V                 |  |  |

| clock period            | 10ns(시뮬레이션에서 6ns 동작)      |  |  |

| chip size               | 5mm x 5mm                 |  |  |

| Operation Mode          | SIMD/MIMD                 |  |  |

| Total Power             | 52.8mW                    |  |  |

| Energy Efficiency       | 121.2MOPS/mW              |  |  |

그림 6. 제작된 HEERP 칩 사진

다. 여기서 121.2MOPS/mW의 결과를 얻었으므로 목표로 하였던 100MOPS/mW급의 재구성형 프로세 서가 개발되었다. 참고로 STARC 로드맵에서 130nm에 대한 예측을 100MOPS/mW로 하고 있다.

# 4.3 HEERP의 에너지효율 향상을 위한 90nm 적용설계

STARC 로드맵에 의하면 90nm 기술에서는 30GOPS의 성능에 100mW 즉, 300MOPS/mW로 예 측되어 있으므로 이에 부응하는 재구성형 프로세서를 개발하려면 HEERP를 개선하여 에너지효율을 높여 야 한다. 이를 위해, 우선 HEERP를 멀티미디어 분야 중 Video 분야에 특화시켜 사용하도록 함으로써 PU 를 종래의 32비트 동작에서 16비트 동작으로 줄일 수 있게 되어 그만큼 칩 사이즈를 줄일 수 있어 보다 저전력을 구현할 수 있게 하였다. 또한 130nm HEERP를 개발할 때 사용하였던 명령어 세트를 개선 하여 에너지효율을 실효적으로 높이는 방안을 사용한 다. 즉, Conditional연산을 1 Cycle 내에 가능하도록 하는 명령어 세트를 개발함으로써 Conditional연산성 능을 향상시키도록 하였다. 예를 들면, 비디오 데이터 처리에 빈도가 높은 MIN, MAX 의 Condition을 부 여하여 처리하는 경우를 명령어 하나로 처리되게 함 으로써 연산 성능 향상이 되도록 한 경우(ARM에서 8 Cycle 소요되던 것을 1 Cycle에 처리)와 Divide와 Round Operation에서 Shift after ALU Opertation을 적용하여 1 Cycle에 가능하도록 함으로써 기존의 방 식(ALU after Shift Operation은 2 cycle 소요)에 비 해 연산효율을 증대시키게 된다. 이렇게 하여 RTL 설계를 진행한 결과는 아래 표 4와 같다. 즉, 에너지 효율이 539MOPS/mW로 나타남을 알 수 있다.

표 4. 90nm 라이브러리를 적용한 합성설계 결과

| Technology        | TSMC 90nm CMOS       |  |  |

|-------------------|----------------------|--|--|

| Synthesis Tool    | DC Ultra             |  |  |

| Clock Period      | 8ns analysis(125MHz) |  |  |

| Total Cell Area   | 4,677,580 unit       |  |  |

| Total Area        | 6.5µm²(Teraform 결과)  |  |  |

| Operation Mode    | SIMD/MIMD            |  |  |

| Total Power       | 119mW                |  |  |

| Energy Efficiency | 539MOPS/mW           |  |  |

#### V. HEERP의 적용

#### 5.1 MP3의 Inverse MDCT에 적용

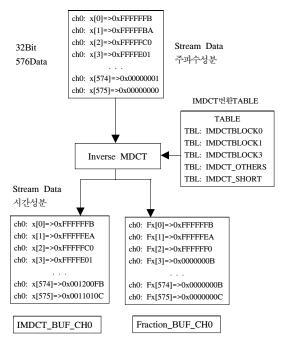

HEERP를 MP3에 응용하는데 IMDCT(Inverse Modified Discrete Cosine Transform)알고리즘을 MP3 디코더에 적용해 보았다. 이것은 MP3디코더에서 IMDCT 연산이 차지하는 비중이 전체의 30%에 해당한다는 점에 착안한 것이다. 즉, IMDCT연산을 HEERP가 감당하고 나머지는 메인프로세서에배당함으로써 IMDCT만큼 메인프로세서의 부담을줄여주는 효과를 볼 수 있다. 아래 그림 7에 IMDCT 연산을 HEERP가 수행하는데 필요한 제반환경을 제공하기 위하여 그림 8과 같이 MP3 디코더 보드를 제작하여 그 동작을 확인하였는데 여기에서는 AMBA인터페이스까지 동작됨을 확인하였다.

그림 7. Inverse MDCT Flow

그림 8. HEERP응용을 위해 제작된 MP3 디코더 보드

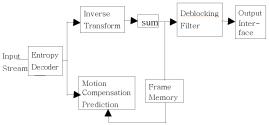

그림 9. MPEG4디코더의 포스트 프로세싱 단계

연산을 위해 그림 7의 알고리즘을 프로그램화하여 사용될 PU들이 할당받은 연산이 수행되도록 프로 그램과 수동 매핑을 시키는 방법을 사용하였다.

# 5.2 MPEG4의 디블로킹 필터(DF)에의 응용

디블로킹 필터는 MPEG4에서 픽셀의 수평/수직 경 계면 에서의 블로킹 현상을 필터링해주는 역할을 수행하는 것인데 위의 MP3 예에서와 같이 이 디블 로킹 필터링(그림 9)을 HEERP를 통해 수행하게 함 으로써 메인 프로세서 의 부담을 감소시켜 주는 역 할을 하게 하였다. 이를 iPROVE라는 에뮬레이터를 사용하여 검증하였는데 사용된 FPGA는 Xilinx Virtex4라서 그 수용용량에 맞추어 PU Array를 4x4에 대해서 적용하였다. 그 결과, ARM만으로 연 산하였을 경우와 비교하여 HEERP의 에뮬레이션 속도가 약 70배 정도 빠른 것으로 확인되었다. 그 이유는 ARM만으로 연산할 경우는 ARM이 전용연 산기 만으로 사용되지는 않으므로(오히려 메인 컨트 롤에 사용되는 빈도가 더 많으므로) 연산효율이 PU 16개를 사용하는 경우보다는 떨어지는 것으로 볼 수 있다. 여기에서도 MP3의 IMDCT알고리즘 처리 와 같이 PU에의 매핑을 수동매핑으로 하였다.

#### 5.3 H.264의 ME블럭에의 응용

H.264의 ME(Motion Estimation)블럭은 H.264에서 변조부에 해당하는 블록인데 이 블록은 영상처

리에 있어 많은 연산량이 요구되는 블록이다. 그러 므로 HEERP를 여기에 적용하여 보았다. PU Array 4x8에 대한 ME에의 적용을 한 모의실험 결과는 다음과 같다. Full Search[-16 +15] 실험을 하면 D1급 30 Frame처리(125MHz동작)에 22,295,347,200 Cycle이 소요되고 처리시간은 약 103.7초가 됨을 확인하였다. 그러므로 D1급 30Frame 처리를 위하여서 HEERP가 효율적으로 메모리에 접근 되게 하고 더 높은 클럭에서 동작할 수 있도록 하는 등의 구조가 개선되도록 해야 할 것이다.

# Ⅵ. 결 론

고에너지효율을 가지는 재구성형 프로세서를 개 발하여 130nm 칩에서 121MOPS/mW의 에너지효율 을 확인하였고 90nm라이브러리를 사용한 시뮬레이 션 결과에서 539MOPS/mW의 에너지효율을 확인하 였다. 이 결과는 STARC에서 예측한 결과를 상회하 는 것으로 재구성형 프로세서의 실제 적용의 길이 마련되었다고 할 것이다. 또한 이들을 MP3디코더 (오디오분야)와 MPEG4, H.264(비디오분야)에 적용 함으로써 그 적용가능성을 확인하였다. 그러므로 모 바일 멀티미디어 적용이 가능한 고에너지효율 재구 성형 프로세서가 개발되었다고 할 것이다. 위의 개 발결과는 다른 재구성형 프로세서와 비교하였을 때 손색이 없고 특히 에너지효율 면에서 우수한 결과 를 보임을 알수 있다(표 5)<sup>[8][9][10]</sup>. 아마도 다른 재 구성형 프로세서들은 에너지 효율 측면에서의 개발 방향은 아니었던 것으로 짐작이 된다(표5에서 보는

표 5. 재구성형 프로세서 상호 비교

|                           | Raw                | Imagine             | Motorola<br>MRC6011 | Morpho-s<br>ys M2  | HEERP              |

|---------------------------|--------------------|---------------------|---------------------|--------------------|--------------------|

| Paralle-<br>lism          | MIMD               | SIMD                | SIMD                | SIMD               | SIMD/<br>MIMD      |

| Max<br>Perfor-<br>mance   | 3.6<br>GOPS        | 23.7<br>GOPS        | 24<br>GOPS          | 28.8<br>GOPS       | 68<br>GOPS         |

| Clock<br>Speed            | 225<br>MHz         | 296<br>MHz          | 250<br>MHz          | 450<br>MHz         | 100<br>MHz         |

| Chip<br>Size              | 18x18mm²           | 12x12mm²            | 31x31mm²            | 16x16mm²           | 5x5mm²             |

| Power                     | 25W                | 4W                  | 3W                  | 4W                 | 53mW               |

| Energy<br>Effici-<br>ency | 0.1<br>MOPS/m<br>W | 12.4<br>MOPS/<br>mW | 8<br>MOPS/<br>mW    | 7.2<br>MOPS/<br>mW | 121<br>MOPS/<br>mW |

| Tech-<br>nology           | 0.15 µm            | 0.15 µm             | 0.13 µm             | 0.13μm             | 0.13 µm            |

바와 같이 다른 재구성형 프로세서들의 전력 소모는 매우 큰 결과로 미루어 보아). 에너지효율을 높이기 위해서는 성능과 전력이 동시에 향상되는 기술이 필요하며 본 논문에서 그러한 시도를 해 보았다. 즉, 본 논문을 통해 모바일 시스템에 적용할 수있는 재구성형 프로세서의 적용가능성은 확인되었다고 할 것이다. 향후에 더 다양한 응용을 통하여최적화된 재구성형 프로세서를 개발한다면 모바일환경에서도 대용량 스트림데이터 처리에 대한 요구가 날로 증대하고 있는 추세에 부응할 수 있을 것으로 보인다. 또한, 여기에서는 다루지 못하였으나비트 스트림데이터를 처리하는전용하드웨어(비트스트림프로세서)를 구성하여 진행해보는 것도 고려해볼만 한 것이 될 것이다.

## 참 고 문 헌

- [1] G.Estrin, "Organization of computer systems— The fixed-plus-variable structure computer," Proceedings of the Western Joint Computer Conference, 1960, pp.30-40.

- [2] Se-Hyeon Kang and In-Cheol Park, "Loosely Coupled Memory-Based Decoding Architecture for Low Density Parity Check Codes," IEEE Custom Integrated Circuits Conference(CICC 2005), San Jose, USA, pp.703-706, 2005, 10.

- [3] S. Ray, Hong Jiang, "A reconfigurable optical bus structure for shared memory multiprocessors with improved performance," *mppoi*, p.108, Second Workshop on Massively Parallel Processing Using Optical Interconnections, 1995.

- [4] Miguel L Silva, J.C.Ferreira, "Using a Tightly-Coupled Pipeline in Dynamically Reconfigurable Platform FPGAs," Proceedings of the 8th Euromicro Conference on Digital System Design, 2005, pp.383-387.

- [5] N. Tabrizi, et al., "A Macro Pipelined Reconfigurable Systems," April 2004 Proceedings of the 1st conference on Computing frontiers, pp.343-349.

- [6] 김남섭 등, "멀티미디어 무선단말기를 위한 재구성 가능한 코프로세서의 설계," 전자공학회 논문지 SD편, 제44권, 제4호, pp.63~72, 2007년 4월

- [7] 안용진 등, "프로세스 네트워크 모델의 정적 분석에 기반을 둔 다중 프로세서 시스템 온 칩 설계공간 탐색," 전자공학회 논문지 SD편, 제44권, 제 10호, 837~846쪽, 2007년 10월.

- [8] M.B. Taylor, et al., "The Raw microprocessor computational fabric for software circuits and general-purpose programs," International Symposium on Microarchitecture, 2002, pp.25-35.

- [9] H. Singh, et al., "Morphosys: An integrated reconfigurable system for data-parallel and computation-intensive application," IEEE Transactions on Computers, v.49, n.5, May, 2000, pp.465-481.

- [10] otorola, "Reconfigurable compute fabric device," Technical Report, 6/2003.

여 순 일 (Soon-il Yeo) 정회원

1983년 2월 경북대학교 전자공학과 졸업

1987년 2월 서강대학교 전자공학과 석사

2005년 2월 한밭대학교 컴퓨터공학과 박사수료

1987년 2월~현재 한국전자통신연구원 재직

1996년 8월 전자응용기술사 취득

<관심분야▷ 전자공학, 컴퓨터 공학, 반도체공학, 통신공학

이 재흥 (Jae-Heung Lee) 정회원 1983년 2월 한양대학교 전자공학과 졸업 1985년 2월 한양대학교 전자공학과 석사 1994년 8월 한양대학교 전자공학과 박사 1989년 7월~현재 한발대학교 컴퓨터공학과 교수 2002년 3월~현재 대전시 정보화정책책임관(CIO) 2007년 2월~2008년 2월 UTD(University of Texas at Dallas) 방문교수 <관심분야> SoC 설계, VLSI CAD, 임베디드시스 템 설계