# 동기화 기능을 가지는 오차보정회로를 이용한 6비트 800MS/s CMOS A/D 변환기 설계

준회원 김 원\*, 정회원 선 종 국\*\*°, 종신회원 윤 광 섭\*\*\*

# Design of a 6bit 800MS/s CMOS A/D Converter Using Synchronizable Error Correction Circuit

Won Kim\* Associate Member, Jong-kug Seon\*\*° Regular Members, Kwang-sub Yoon\*\* Lifelong Member

요 약

본 논문에서는 무선 USB 칩-셋 내 무선통신시스템단에 적용될 수 있는 6비트 800MS/s 플래쉬 A/D 변환기를 설계하였다. 기존의 A/D 변환기에서 서로 독립적으로 사용되던 오차보정회로단과 동기화단을 하나의 회로로 간소화 시켜서, 하드웨어에 대한 부담을 감소시켰다. 제안한 오차보정회로는 기존의 오차보정회로보다 MOS 트랜지스터의 수를 5개 감소시킬 수 있으며, 오차보정회로 한 개당 면적은 9% 정도 감소하게 된다. 설계된 A/D 변환기는 0.18µm CMOS 1-poly 6-metal 공정으로 제작되었으며 측정 결과 입력 범위 0.8Vpp, 1.8V의 전원 전압에서 182mW의 전력소모를 나타내었다. 800MS/s의 변환속도와 128.1MHz의 입력주파수에서 4.0비트의 ENOB을 나타내었다.

Key Words: ADC(Analog-to-Digital Converter), Flash, Error Correction Circuit

#### **ABSTRACT**

The paper proposes the 6bit 800MS/s flash A/D converter that can be applied to wireless USB chip-set. The paper simplified the error correction circuit and synchronization block as one circuit which are used respectively, and furthermore reduced the burden on the hardware. Comparing to the conventional error correction circuit, the proposed error correction circuit in this paper reduced 5 MOS transistors, the area of each error correction circuit is reduced by 9%. The A/D converter is fabricated with 0.18um CMOS 1-poly 6-metal process, and power dissipation is 182mW at 0.8Vpp input range and 1.8V supply voltage. The measured result shows 4.0bit of ENOB at 800MS/s conversion rate and 128.1MHz input frequency.

# Ⅰ. 서 론

USB(Universal Serial Bus)는 사용의 편리성, 확장성을 기반으로 PC 역사상 가장 성공적인 접속 장치로서, 현재까지 20억 개 이상이 사용되고 있고, USB가장착된 장치의 종류 및 사용 개수도 빠르게 증가하는

추세이다. 이와 같은 USB의 발전에 힘입어 유선의 속도와 보안성에 무선의 편리함을 추가한 무선 USB는 근래에 핫 이슈로 부상하고 있다.<sup>[1]</sup> 무선 USB 통신시스템내의 무선부에는 광대역의 주파수대를 복수의 밴드로 분할해, 그것을 묶어 전송 속도를 높인 '초광대역(Ultra Wide Band)' 통신 방식을 채용한다. 초광대역(Ultra Wide Band)' 통신 방식을 채용한다. 초광대

<sup>※</sup> 본 연구는 지식경제부 및 정보통신연구진흥원의 대학 IT연구센터 지원 사업의 연구결과로 수행되었음. (NIPA-2010-C1090-1011-0007)

\* LG전자 MC사업부, \*\* LS 산전, (°: 교신저자), \*\*\* 인하대학교 전자공학과 정보전자 공동 연구소 논문번호: KICS2010-01-018, 접수일자: 2010년 1월 12일, 최종 접수일자: 2010년 4월 19일

역 통신단은 크게 RF단과 기저대역단으로 나뉘며, 기 저대역단내의 수신기에는 변환속도 500MS/s 이상의 고속 A/D 변환기가 사용된다. 그러나 이러한 고속 A/D 변환기의 CMOS 구현을 위해서는 초고속 CMOS 회로설계 기법, 하드웨어 복잡도, 저전력화 등 해결해야 할 문제들이 있다.<sup>[2]</sup>

플래쉬 A/D 변환기에 사용되는 비교기는 고속의 클릭에 동기화 되어 초기화와 비교를 빠르게 반복하는 래치 타입이 사용된다. (3) 이러한 비교기는 수GHz의 클릭에서도 동작할 수 있지만, 클릭에 의한 스위칭노이즈, 비교기의 meta-stability 등에 의해 출력에 버블에러가 발생할 수 있게 된다. 따라서 버블에러 보정회로 또는 오차보정회로를 사용하여 비교기의 버블에러를 제거시키는 과정이 필요하다.

기존의 플래쉬 A/D 변환기에는 3-gate AND로 이루어진 오차보정회로와 동기화를 위한 플립-플롭단을 독립적으로 사용하였다.<sup>[4]</sup> 이 때 사용되는 오차보정회로단과 동기화단은 모든 비교기의 뒤에 사용되어야하기 때문에 전체 회로의 복잡도를 증가시키는 원인이 된다.

제안한 플래쉬 A/D 변환기에서는 기존의 오차보정 회로와 동일한 기능을 하면서, MOS 트랜지스터 수를 감소시킨 오차보정회로를 사용하여 A/D 변환기 전체 의 회로 복잡도 및 소자수를 감소시켰다. 또한 저항을 이용한 인터폴레이션 기법을 사용하여 전단 증폭기 수를 감소시켰으며 소비전력과 면적이 최소화 되도록 설계하였다.

II장에서는 제안하는 A/D 변환기의 구조와 오차보 정회로에 대해 설명하였다. III장은 제작된 A/D 변환 기의 레이아웃에 대해 설명하고, IV장은 제안한 6비 트 A/D 변환기의 측정 결과를 기술하였다. 그리고 V 장에서는 결론을 맺었다.

# Ⅱ. 제안한 6비트 A/D 변환기의 설계

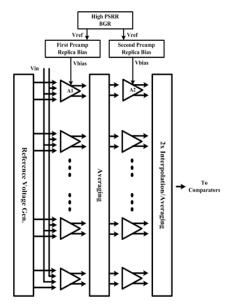

본 논문에서 제안하는 6비트 A/D 변환기의 아날로 그 전단부를 그림 1에 나타내었다. 플래쉬 구조는 모든 양자화 레벨과 아날로그 입력 신호가 비교되는 방식으로 한 클럭 사이클에 N비트의 분해능을 갖는 디지털 코드로 변환되므로 가장 빠른 구조이다.<sup>[5]</sup> 제안한 A/D 변환기는 기준전압을 위한 저항열, 1차/2차전단증폭기단, 레플리카 바이어스단, 저항평준화/인터폴레이션단으로 구성되었다.

플래쉬 A/D 변환기가 가지는 단점인 큰 전력소모 를 줄이기 위해서 전단 증폭기의 출력에 저항을 이용

그림 1. 6비트 플래쉬 A/D 변환기의 아날로그 전단부 Fig. 1. Analog front-end of the proposed A/D Converter

한 인터폴레이션 기법이 적용되었다. [6] 저항을 사용하여 두 신호의 중간 값을 얻게 되며, 별도의 전단 증폭기를 사용하지 않고, 1개의 추가적인 비교기 입력 신호를 생성한다. 1차 전단 증폭기와 2차 전단 증폭기를 이용하여 상위 1비트 양자화를 하였고, 총 6비트의 해상도를 구현하기 위해서 2단 전단 증폭기의 출력에 2배 인터폴레이션 기법을 적용하였다. 저항을 이용한인터폴레이션 기법은 저항 평준화 효과도 나타나므로 A/D 변환기의 선형성을 향상시킬 수 있다. [7]

한편, 공정, 공급전압, 온도 등의 변화로 전단증폭기의 전압 이득과 출력 스윙 폭이 원하는 레벨로 유지되지 못할 수 있다. 특히 고속의 A/D 변환기의 입력단으로 이용되는 전단증폭기는 전압 이득이 작고 대역폭이 매우 크므로 PVT(Process, Voltage, Temperature) 변화에 더욱 민감할 수 있어 A/D 변환기 전체 특성에큰 영향을 줄 수 있다. 따라서 본 연구에서는 전단증폭기인 완전 차동 증폭기의 전류원 바이어스 전압을레플리카 바이어스 회로를 이용하여 생성하였다.[8]

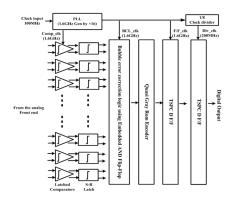

제안하는 A/D 변환기의 디지털 후단부를 그림 2에 나타내었다. 고속 래치 비교기, S-R 래치회로, 동기화 기능을 가지는 오차보정회로, 인코더, 그리고 플립-플롭으로 구성되었다. 또한 테스트 보드로 성능 검증시 칩 외부에서 수 백MHz의 클럭을 칩 내부로 왜곡 없이 공급하는 것이 불가능하기에, 내부에 PLL(Phase Locked Loop)회로를 온칩 시켜 50MHz의 외부 기준 클럭을 내부에서는 800MHz로 체배 시

그림 2. 6비트 플래쉬 A/D 변환기의 디지털 후단부 Fig. 2. Digital back-end of the proposed A/D Converter

켰다. 또한 디지털 출력 정보를 로직 분석기에서 추출 하기 위해서 출력단에 1/8 분주회로를 이용하여 100MHz에 동기화 될 수 있도록 하였다.

A/D 변환기에 사용되는 비교기단은 2차 전단증폭기단 출력을 입력으로 한다. 6비트의 해상도를 위해총 63개의 비교기가 이용되어 A/D 변환기에서 많은하드웨어를 차지한다. 따라서 비교기는 작은 하드웨어로 구성되어 6-비트의 해상도와 1GHz 이상의 고속동작이 가능하여야 한다. 고속 동작을 만족하기 위해비교기는 증폭기 구조가 아닌 클럭에 의해 리셋-프리차지가 빠르게 반복되는 래치형 구조가 사용된다.<sup>[3]</sup>

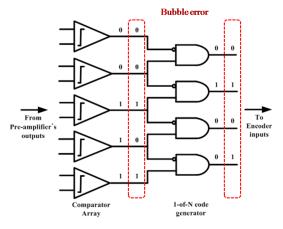

플래쉬 A/D 변환기에서 비교기 다음의 출력은 온도계 코드 형태이지만 여러 오차 요인으로 그림 3 과 같이 온도계 코드의 '0' 코드의 나열 중에 '1'이 하나 발생하는 경우가 있는데, 이것을 버블(bubble), 혹인스파클(sparkle)이라고 한다. 특히 버블은 비교기가 클 럭에 동기되어 전환하는 때에 비교기의 meta-stability,

그림 3. 버블에러 발생의 예 Fig. 3. Example of bubble error

노이즈, 대역폭 제한 등의 이유로 많이 발생한다. 이를 위해 그림 4 와 같이 3-입력 AND 게이트를 사용하여 1-of-n 코드로 전환하는 과정에서 1비트의 버블에러를 보정할 수 있다.<sup>[4]</sup> 그러나 이러한 회로는 로직을 통과하면서 지연시간 차이가 발생하게 되고, 바로 뒷단에 동기화를 시킬 수 있는 플립-플롭 회로가 사용된다. 이러한 오차보정회로는 플래쉬 A/D 변환기의해상도가 n비트 인 경우 2<sup>n</sup>-1개가 사용되어 소비전력및 하드웨어 또한 지수 함수적으로 증가하게 된다. 따라서 오차보정의 기능을 수행하면서, 하드웨어를 줄일수 있는 회로가 필요하다.

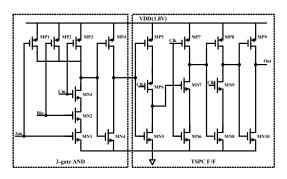

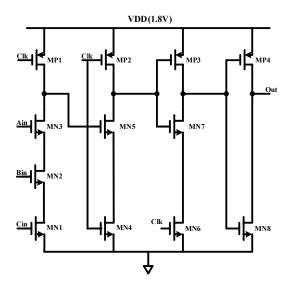

제안한 오차보정회로를 그림 5 에 나타내었다. MP1, MN1, MN2, MN3로 구성된 Clocked 3-gate NAND와 MP2, MN4, MN5로 구성된Clocked 인버 터에 의해 3-gate AND 로직이 결정되며, MP3, MN6,

그림 4. 기존의 오차보정회로

Fig. 4. Conventional error correction circuit

그림 5. 동기화 기능을 가지는 오차보정회로 Fig. 5. Synchronizable error correction circuit

MN7로 구성된 3-state 인버터에 의해 동기화가 진행된다. 이러한 MOS 트랜지-스터 구성을 통해 제안하는 오차보정회로는 3개의 입력을 받아서 3-gate AND의 기능을 하면서 동시에 공급되는 클럭에 동기화 될수 있게 된다.

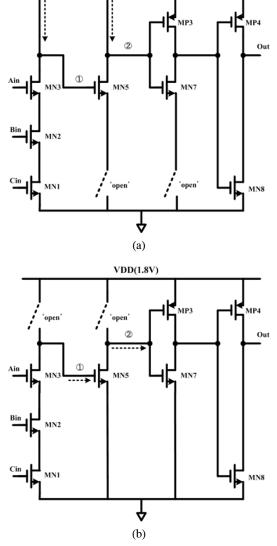

그림 6 에는 공급되는 클럭이 High 또는 Low 일 때, 제안하는 오차보정회로의 등가회로도를 나타내었다.

먼저 그림 6 (a) 와 같이 클릭이 'Low'일 때에 오 차보정회로는 프리-차지 동작을 한다. 즉, 3개의 입력

VDD(1.8V)

그림 6. 공급되는 클럭이 (a) Low, (b) High 일 때 제안한 오차보정회로의 등가회로도

Fig. 6. The equivalent circuit of proposed error correction circuit in that clock is (a) Low or (b) High

이 들어오더라도 1번 노드와 2번 노드에는 항상 VDD 가 연결되어 있으며, 전하가 충전되는 기능을 수행하 게 된다.

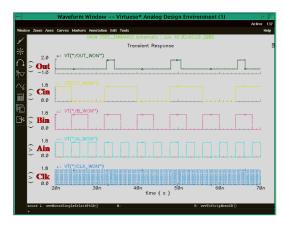

다음으로 그림 6 (b) 와 같이 클럭이 'High'일 때에 오차보정회로는 다이나믹 구조의 로직으로 동작한다. 클럭이 High가 되는 순간 1번 노드와 2번 노드에 충전된 전하가 해당 로직에 따라 다음. 단으로 이동하게되며 수 GHz의 클럭에서도 해당 로직의 결과를 출력으로 내보내게 된다. 그림 7 에는 제안하는 오차보정회로에 세 개의 디지털 입력과 1.6GHz의 클럭을 입력했을 때, 로직의 기능과 동기화 기능이 정상적으로 되는지 모의 실험한 결과이다. 1.6GHz의 고속 클럭에서도 3-gate AND 로직을 수행하며, 클럭에 동기화 되는 것을 확인할 수 있다.

제안하는 오차보정회로와 기존의 오차보정회로<sup>[4]</sup>를 세 가지의 성능 변수 '소비 전력', '지연시간 시간', '면적' 에 따라 성능을 비교하였다. 모의 실험한 결과를 표 1 에 정리하였다.

그림 7. 제안한 오차보정회로의 출력파형

Fig. 7. Output of proposed error correction circuit

표 1. 기존의 오차보정회로와 제안한 오차보정회로의 성능 비교

Table 1. Comparison of conventional and proposed error correction circuit

| 성능 변수   | 기존의<br>오차보정회로                | 제안하는<br>오차보정회로               |

|---------|------------------------------|------------------------------|

| 트랜지스터 수 | 17개                          | 127}                         |

| 면 적     | 345um <sup>2</sup>           | 314um <sup>2</sup>           |

| 지연시간 시간 | Tr=28.69psec<br>Tf=22.11psec | Tr=28.62psec<br>Tf=22.07psec |

| 소비 전력   | 4.88mW                       | 4.92mW                       |

먼저 회로를 구성하는 트랜지스터의 수의 경우 기존의 오차보정회로에서는 17개가 필요한 반면, 제안하는 오차보정회로는 12개의 트랜지스터로 구성된다. 이러한 트랜지스터의 수 감소는 A/D 변환기를 칩으로구현 시 면적이 감소하게 되며, 동일한 공정에서 제안하는 오차보정회로 면적은 기존의 오차보정회로 면적보다 약 9% 정도 감소하게 된다.

지연시간(Propagation delay)의 경우는 클럭 샘플링 속도 Fs=1.6GHz(Ts=625psec)을 기준으로 디지털출력 파형의 상승 시간과 하강 시간을 관찰하였다. 모의실험 결과 지연시간 시간은 거의 차이가 없는 것을확인할 수 있다. 지연시간은 최종 출력단의 로직에 의해 결정되는데, 기존의 오차보정회로와 제안하는 오차보정회로의 최종 출력단은 모두 CMOS형 인버터이기때문이다.

마지막으로 소비전력의 경우 오차보정회로는 클럭을 기반으로 하는 회로이기에 다음의 수식 (1) 에 의하여 주파수(스위칭 수) 성분을 고려해야 한다.

$$P_{diss} \propto C_L \cdot f_s \cdot V^2$$

(1)

공급 전압은 동일하기에 특정 시간 동안의 동일한 클럭을 공급 하였을 때, 동적 소비전력을 관찰해 보았 다. 샘플링 주파수 조건은 Fs=1.6GHz 이며, 시간은 0~100nsec 까지 로직 동작을 하였을 때의 소모 전력 이다. 모의 실험 결과 제안하는 오차보정회로를 사용 시, 기존의 오차보정회로보다 0.9% 정도 소비전력이 증가함을 확인할 수 있었다. 기존의 오차보정회로의 경우 전체가 CMOS 형태의 구성이며, Low나 High의 로직이 입력되면 NMOS나 PMOS의 트랜지스터는 둘 중 하나는 무조건 off가 되어 VDD에서 GND까지 전 류 path가 차단된다. 따라서 기존의 오차보정회로에서 는 정적 전류(static current)가 흐르지 않으며, 스위칭 시 발생하는 동적 전류(dynamic current)만 발생하여 소모 전력이 매우 낮다. 반면 제안하는 오차보정회로 는 그림 6 (a)와 같이 클럭이 Low일 때, MN1, MN2, MN3에는 VDD에서 GND까지 전류 path가 형성된다. 이러한 path는 Ain, Bin, Cin에 모두 High가 입력될 때 정적 전류를 흐르게 함으로써, 전체 동적 소비전력 증가에 기여하게 된다.

#### Ⅲ. 6비트 A/D 변환기 레이아웃

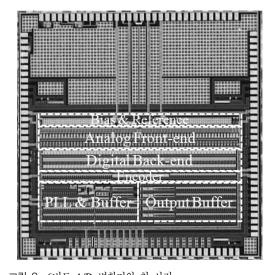

설계한 A/D 변환기의 레이아웃은 고속 동작 시 발

생하는 잡음을 억제하기 위해 완전 대칭 구조를 택하였다. 실제 레이아웃은 CMOS 0.18 $\mu$ m 1-poly 6-metal 공정을 이용하여 구현하였으며, 구현한 6비트 A/D 변환기의 칩 사진을 그림 8 에 나타내었다.

레퍼런스 생성 단부터 제 2 전단 증폭기까지 아날로그 블록이며 비교기부터 인코더까지 디지털 블록에 해당된다. 아날로그 블록과 디지털 블록을 더블 가드링을 이용해 분리하였고, 전원부 또한 아날로그와 디지털을 서로 분리하여 디지털 단에서 발생하는 잡음이 아날로그 단에 미치는 영향을 최소화 하였다. 또한 레퍼런스 생성단의 저항에는 바이패스 MOS 커패시터를 집적함으로써 레퍼런스 전압이 변동되는 것을 억제하였다.

레이아웃 결과 제작된 6비트 A/D 변환기의 유효 칩 면적은 3.64mm²(2.6mm x 1.4mm)이다.

그림 8. 6비트 A/D 변환기의 칩 사진 Fig. 8. Chip photo of 6bit A/D converter

#### Ⅳ. 측정 결과 및 고찰

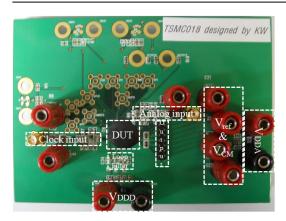

본 논문에서 구현된 A/D 변환기의 성능은 그림 9에 나타낸 테스트 보드를 사용하여 측정했다. 디지털 블록과 아날로그 블록을 완전히 분리 시켰으며, 아날 로그 블록을 디지털 노이즈로부터 보호하기 위해 아날로그 파워와 디지털 파워를 분리하였다.

아날로그 입력을 위한 SMA와 싱글 신호를 차동신 호로 만들어주기 위한 트랜스포머를 사용하여 입력단 을 구성하였다. 칩을 구성하는 패키지에 생기는 기생 인덕터와 커패시터의 영향으로 고속 클럭 신호의 전 달이 어렵기 때문에 아날로그 신호와 마찬가지로 차

그림 9. 제작한 6비트 A/D 변환기의 테스트 보드 Fig. 9. Test board for 6bits A/D converter

동으로 만들어 줄 수 있도록 트랜스포머를 사용하였다. A/D 변환기의 디지털 출력은 로직분석기에 연결하기 쉽도록 핀을 사용하여 구성하였다.

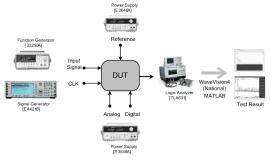

설계한 A/D 변환기의 성능 측정을 위한 측정 환경을 그림 10에 나타내었다. 파형 발생기 (33250A)와 신호 발생기 (E4421B)를 이용하여 아날로그 입력 신호와 클릭 신호를 인가하였다. 전원공급기(E36 46A)로 전원 전압을 공급하였으며, A/D 변환기의 출력을 수집하기 위하여 로직분석기 (TLA601)을 사용하였다.

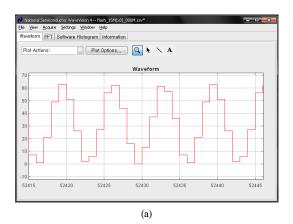

로직분석기를 통해 수집한 데이터를 National Semiconductor사의 WaveVision4 분석 프로그램을 이용해 FFT(Fast Furier Transformation)분석을 시행하였으며, 입력 주파수에 따른 하모닉 성분들을 검출하였다. 그림 11에는 내부의 샘플링 주파수가 800MHz(외부의 샘플링 주파수 = 100MHz)이고, 아날로그 입력 주파수가 128.4MHz(외부의 입력 주파수 = 16.05MHz)일 때, 복원 파형과 측정한 신호 스펙트럼을 나타내었다. 측정 결과 제작된 A/D 변환기는 29.05dBc의 SFDR(Spurious Free Dynamic Range), 4.0비트의 ENOB(Effective Number Of Bit)를 보였다.

그림 10. 6비트 A/D 변환기 측정 환경 Fig. 10. Measurement environment for 6bits A/D converter

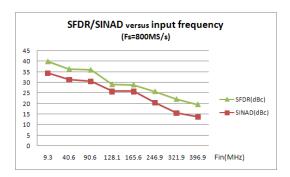

내부의 샘플링 주파수 800MHz에서 아날로그 입력 주파수의 변화에 따른 SFDR과 SINAD(Signal to Noise ratio and Distortion)을 그림 12 에 나타내었다. 246.9MHz의 높은 입력 주파수에서도 25dBc 이상의 SFDR을 나타내었다.

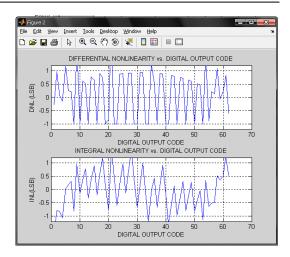

설계한 A/D 변환기의 정적 성능을 나타내는 DNL/INL에 대한 그래프를 그림 13 에 나타내었다. DNL(Differential Non-Linearity)은 인접한 두 개의 코드간의 단조증가성을 측정하게 되며, INL(Integral Non-Linearity)은 이상적인 코드와 실제 코드간의 선형성을 측정하게 된다.<sup>[9]</sup> 로직 분석기에서 추출된 데이터를 기반으로 매트랩의 히스토그램 분석 방법<sup>[10]</sup>을이용하여 결과를 얻었다. 측정 결과 DNL은 -1.0/+1.2 LSB, INL은 -1.2/+1.3 LSB으로 나타났다.

제안하는 A/D 변환기의 측정 결과를 표 2 에 요약 하였다. 기존의 A/D 변환기와 비교했을 때, 제안하는 A/D 변환기가 가지는 특징은 소형화 및 회로복잡도의

그림 11. 측정된 (a) 복원파형과 (b) 신호 스펙트럼 (Fdown.s =100MHz, Fin=16.05MHz) Fig. 11. Measurement results of (a) reconstructed

signal and (b) signal spectrum.

그림 12. 입력주파수 변화에 대한 SFDR/SINAD Fig. 12. SFDR/SINAD versus input frequency

표 2. 제안한 A/D 변환기의 측정 결과 요약 Table 2. Measurement results of A/D converter

|                   | Measurement Result                                                                                                   |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------|--|

| Sampling Freq.    | 800 Msamples/s                                                                                                       |  |

| Resolution        | 6 bit                                                                                                                |  |

| Input Range       | 0.8 Vpp Differential                                                                                                 |  |

| Process           | CMOS 0.18um n-well                                                                                                   |  |

| Supply Voltage    | 1.8 V                                                                                                                |  |

| SFDR/ENOB         | 39.9dBc/5.4bit@fin=9.3MHz<br>36.3dBc/4.9bit@fin=40.6MHz<br>36.0dBc/4.8bit@fin=90.6MHz<br>29.1dBc/4.0bit@fin=128.1MHz |  |

| DNL               | -1.0/+1.2 LSB                                                                                                        |  |

| INL               | -1.2/+1.3 LSB                                                                                                        |  |

| Power Dissipation | 182 mW                                                                                                               |  |

| FoM               | 5.39pJ/step                                                                                                          |  |

| Chip Area         | 3.64mm <sup>2</sup> (2600um×1400um)                                                                                  |  |

감소이다. 제안하는 오차보정회로는 기존의 오차보정 회로보다 소비전력이 0.9% 정도 증가하지만, 오차보 정회로 한 개당 면적이 9% 정도 감소하게 됨으로써 제안하는 오차보정회로단의 면적은 기존의 오차보정 회로단의 것보다 1953um² 정도 감소하게 된다. 따라서 제안하는 A/D 변환기는 집적화와 작은 하드웨어를 요구하는 모바일 어플리케이션(mobile application)이나 포터블 디바이스(portable device)에 유용하게 사용될 수 있을 것이라 기대된다.

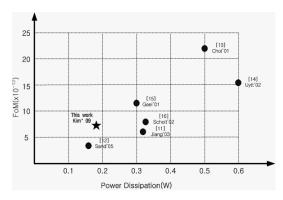

제안한 6비트 A/D 변환기와 동일한 해상도의 고속 A/D 변환기의 성능을 비교한 결과를 그림 14 에 나타내었다. 성능 비교는 A/D 변환기의 해상도 및 변환속도 대비 소모된 전력을 나타내는 지표인 FoM(Figure of Merit) 식 (2)을 이용하였다.<sup>[11]</sup> 여기서 n은 A/D 변환기의 ENOB(유효비트수)를 의미한다.

그림 13. DNL/INL 측정결과 Fig. 13. Measured DNL/INL

그림 14. 제안한 A/D 변환기와 동해상도 고속 A/D 변환기 와의 비교

Fig. 14. Comparison of FoM between the proposed A/D converter and commercial A/D converters

$$FoM = \frac{\text{소비전력}}{2^n \cdot \text{변환속도}} [Joul/step]$$

(2)

제안한 6비트 A/D 변환기는 기존의 A/D 변한기와 비교하였을 때, 전력소모 면에서 우수한 성능을 보이 지만, 변환속도와 유효비트수가 다소 낮은 성능을 보이 기 때문에 전체적으로 중간정도의 FoM을 나타낸다.

#### V. 결 론

본 논문에서는 동기화 기능을 가지는 오차보정회로를 이용하여 6비트 800MS/s A/D 변환기를 설계 및 구현하였다. 오차보정회로는 고속 비교기에서 발생하는 버블에러를 제거할 수 있기에 고성능의 플래쉬

A/D 변환기에 필수적으로 사용되는 회로이다. A/D 변환기내 모든 비교기의 뒤에 사용되는 오차보정회로의 하드웨어 복잡도를 감소시켜서 전체 회로의 구성소자의 수를 줄이고, 회로 복잡도를 줄일 수 있었다. 제안하는 A/D 변환기는 TSMC 0.18um n-well 1-poly 6-metel CMOS 공정으로 제작되었으며, 측정결과 1.8V 단일 전원 전압에서 182mW의 전력 소모를 보였다. 또한 800MHz의 샘플링 주파수와 128.1MHz 입력 주파수에서 SFDR 및 ENOB는 각각 29.0dBc, 4.0 비트 수준을 보인다. 제작된 A/D 변환기의 칩 면적은 3.64mm² 이다.

#### 참 고 문 헌

- [1] Brad Hosler, "Certified Wireless USB," Certified WIreless USB Developers Conference, Oct 2007.

- [2] Lalitkumar Y. Nathawad, Ryohei Urata, Bruce A. Wooley, David A. B. Miller, "A 40-GHz-Bandwidth, 4-bit, Time-Interleaved A/D Converter Using Photoconductive Sampling," *IEEE J. Solid-State Circuits*, Vol.38, pp.2021-2030, Dec 2003.

- [3] Pedro M. Figueiredo, Joao C. Vital, "Kickback Noise Reduction Technique for CMOS Latched Comparator," *IEEE Tran. Circuit Syst.* II, Vol.53, No.7, Jul 2006.

- [4] B. Razavi, Principles of Data Conversion System Design, IEEE Press, 1995.

- [5] Jeny (Heng-Chih) Lin, Babet Hatoun, "An Embedded 0.8V/480uW 6B/22MHz Flash ADC in 0.13-um Digital CMOS Process Using a Nonlinear Double Interpolation Technique," *IEEE J. Solid-State Circuits*, Vol.38, pp.1610-1617, Dec 2002.

- [6] Hui Pan, Asad A. Abidi, "Spatial Filtering in Flash A/D Converter," *IEEE Tran. Circuit Syst.* II, Vol.50, No.8, pp.208-211, Aug 2003.

- [7] Klaas Bult, Aaron Buchwald, "An Embedded 240-mW 10-b 50-MS/s CMOS ADC in 1-mm<sup>2</sup>," *IEEE J. Solid-State Circuits*, Vol.32, No.12, pp.1887-1895, Dec 1997.

- [8] S. C. Heo, Y. C. Jang, S. H. Park and H.J. Park, "An 8-bit 200MS/s CMOS

- folding/interpolating ADC with a Reduced Number of Preamplifiers Using an Averaging Technique," *Proceedings on IEEE ASIC/SOC Conference*, pp.80-83, Sept. 2002.

- [9] Phillip E. Allen and Douglas R. Holberg, CMOS Analog Circuit Design, Oxford University Press Inc, 2002.

- [10] Francisco Andre Cottea Alegria, Antonio Manuel da Cruz Serra, "Overdrice in the Ramp Histogram Test of ADCs," *IEEE Tran. Instrumentation and Measurement.*, Vol.54, No.6, Dec 2005.

- [11] X. Jiang, Z. Wang, M. F. Chang, "A 2GS/s 6b ADC in 0.18um CMOS," *IEEE Int. Solid-State Circuits Conf. Dig Tech. Papers*, pp.322-323, Feb 2003.

- [12] Christoph Sandner, Martin Clara, Andreas Santner, Thomas Hartig, Franz Kuttner, "A 6-bit 1.2-GS/s Low-Power Flash-ADC in 0.13um Digital CMOS," *IEEE J. Solid-State Circuits*, Vol.40, pp.1499-1505, Jul 2005.

- [13] M. Choi, A. A. Abidi, "A 6-b 1.3-Gsample/s A/D converter in 0.35um CMOS," *IEEE J. Solid-State Circuits*, Vol.36, No.12, pp.1847-1858, Dec 2001.

- [14] K. Uyttemhove, M. Steyaert, "A 1.8-V 6-bit 1.3-GHz flash ADC in 0.25um CMOS," *IEEE J. Solid-State Circuits*, Vol.38, No.7, pp.1115-1122, Jul 2003.

- [15] G. Geelen, "A 6b 1.1 GSample/s CMOS A/D converter," *IEEE Int. Solid-State Circuits Conf. Dig Tech. Papers*, pp.128-129, Feb 2001.

- [16] P. Scholtens, M. Vertregt, "A 6-b 1.6-Gsample/s flash ADC in 0.18-um CMOS using averaging termination," *IEEE J. Solid-State Circuits*, Vol.37, No.12, pp.1599-1609, Dec 2002.

## 김 원 (Won Kim)

2008년 2월 인하대학교 전자 공학과 학사 2010년 2월 인하대학교 전자

2010년 2월 인하대학교 전자공학과 석사

2010년 2월~현재 LG전자 MC사업부 연구원 <관심분야> 아날로그 VLSI 설계, 플래쉬 A/D 변환기 설계

## 선 종 국 (Jong-kug Seon)

정회원

1993년 2월 인하대학교 전자 공학과 학사

1995년 2월 인하대학교 전자 공학과 석사

2000년 2월 ENST(Ecole Nationale Superieuredes Telecommunications) France, 전 자통신공학과 박사 졸업

2000년~2003년 Nortel Networks, UK, RF/Analog IC Design Engineer 2004년~현재 LS산전 중앙 연구소 책임연구원 <관심분야> PLL 설계, A/D 및 D/A 변환기 설계, RF 설계

#### 윤 광 섭 (Kwang-sub Yoon)

종신회원

1982년 2월 인하대학교 전자 공학과

1983년 2월 Georgia Institute Inc, Technology 전자공학 석사

1989년 2월 Georgia Institute Inc, Technology 전자공학 박사

1984년 3월~1989년 2월 Georgia Institute of Technology Research Assistant

1989년 3월~1992년 2월 Silicon Systems Inc, Tustin Calif. U.S.A Senior Design Engineer

1992년 3월~현재 인하대학교 전자공학과 교수

<관심분야 혼성신호처리 집적회로 설계, 설계 자동화 및 소개회로/시스템 모델링 등