**DB**Pia

# 고기동 유도무기를 위한 HWIL 시뮬레이션 제어 시스템 개발 연구

정회원 김 운 식\*, 이 병 선\*, 종신회원 김 상 하\*\*°

# A Study on the Development of HWIL Simulation Control System for High Maneuver Guided Missile System

WoonSik Kim\*, ByungSun Lee\* Regular Members, SangHa Kim\*\*\* Lifelong Member

요 약

고기동 유도탄들은 다양한 탄내 인터페이스와 빠른 유도 조종 루프를 가진다. 그러므로 Hardware-in-the-Loop(HWIL) 시뮬레이션 제어 시스템은 고성능의 연산기능 및 하드웨어 인터페이스 기능을 가져야 하며, 실시간 운영체제, 임베디드 시스템, 자료 통신, 실시간 하드웨어 제어와 같이 다양한 IT 분야를 융합하여 개발되어야 한다. 이 논문은 고기동 유도탄의 HWIL 시뮬레이션을 수행하기 위한 제어 시스템 설계 기법으로 시스템 하드웨어 구성, 고성능의 다중 프로세서를 사용하기 위한 업무 할당 알고리즘, HWIL 시뮬레이션 실시간 연산 및 제어 기법, 프로세서 통신 기법, 실시간 자료 획득 기법을 제시한다.

Key Words: HWIL Simulation Control system, Real-Time Missile Simulation, Data acquisition

#### **ABSTRACT**

The High maneuver missiles use various interfaces and high speed guidance and control loop. Hardware-in-the-Loop(HWIL) simulation control system, therefore, should have high performance computing power and hardware interface capabilities, and should be developed using IT technology with which real time operating system, embedded system, data communication technology, and real time hardware control are integrated. This paper suggests the control system design techniques, such as a system hardware configuration, a job distribution algorithm for high performance multi-processors, a real time calculation and control mechanism, inter-processor communication mechanism, and a real time data acquisition technique, to perform the HWIL simulation for high maneuver missile system.

### I. 서 론

현대의 유도무기체계는 다양한 표적 탐지 및 추적 센서(적외선, 초고주파)를 사용하여 정밀한 유도 제어를 수행하는 복잡한 유도무기체계로 발전하고 있다<sup>[1,2]</sup>. 이와 같은 복잡한 유도무기체계들은 개발 과정에서 많은 시스템 오류들을 포함할 수 있으므로 유도탄

부체계 하드웨어와 탑재 소프트웨어를 검증하고 입증하는 과정이 필수적이며 Hardware-in-the-Loop (HWIL) 시뮬레이션이 중요한 시험 기법으로 이용되고 있다.

HWIL 시뮬레이션은 유도탄 부체계 소프트웨어 모델, 유도탄 6자유도 비행운동 모델, 실제 유도탄 부체계 하드웨어와 초고주파 신호 모의 시스템(Radio

<sup>\*</sup> 국방과학연구소(wskim0106@hanmail.net, zeekzion@naver.com),

<sup>\*\*</sup> 충남대학교 컴퓨터공학과 컴퓨터네트워크 연구실(shkim@cnu.ac.kr) (°: 교신저자) 논문번호: KICS2010-07-346, 접수일자: 2010년 7월 31일, 최종논문접수일자: 2010년 10월 14일

Frequency Simulation System(RFSS)<sup>[1]</sup>), 비행자세모 의기와 같은 HWIL 시뮬레이션 시험 장비들이 실시간으로 연동된 환경에서 수행된다. 따라서 실시간 시뮬레이션을 통합적으로 제어하기 위한 제어 시스템이 필수적이다. 특히 고기동의 유도탄에 대해서는 복잡한소프트웨어 모델의 실시간 연산, 유도탄 부체계와 시험 장비와의 실시간 통신 인터페이스, 시뮬레이션 결과 분석을 위한 시뮬레이션 자료 획득 기능이 포함된고성능의 시뮬레이션 제어 시스템이 필요하다.

이 논문에서는 고기동 유도탄의 HWIL 시뮬레이션 에 적용될 수 있는 HWIL 시뮬레이션 제어 시스템 설 계 기법을 제안하고, 실제 구현한 시스템의 예와 성능 을 제시한다.

이 논문은 다음과 같이 구성되어 있다. 2장에서는 HWIL 시뮬레이션 환경 구현 방법과 관련 연구를 소개하며, 3장에서 고기동 유도탄 HWIL 시뮬레이션을 수행하기 위한 HWIL 시뮬레이션 제어 시스템 개발기법을 제시하고, 4장에서 개발 결과를 설명하며, 5장에서 결론을 제시한다

### Ⅱ. HWIL 시뮬레이션 환경 구현 및 관련 연구

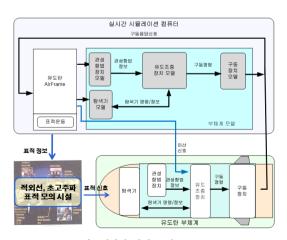

일반적으로 유도탄은 탐색기, 관성항법장치, 유도 조종장치, 구동장치와 같은 복잡한 유도조종 부체계를 가진다. 유도탄 시스템의 성능 평가를 위한 HWIL 시 뮬레이션 환경은 실제 유도탄 부체계, 유도탄 6자유도 비행운동 모델, HWIL 시뮬레이션 시험 장비들을 연 동하여 그림 1과 같이 구성하게 된다.

HWIL 시뮬레이션은 이와 같이 실제 하드웨어와 소프트웨어 모델을 연동하여 시간 연속적인 시뮬레이 션 루프를 형성함으로써 실제 비행환경을 실험실에서

그림 1. HWIL 시뮬레이션 환경 구성

모의하여 수행한다. HWIL 시뮬레이션 시험장비들은 유도탄 부체계가 사용하는 탐색기에 종류에 따라 초고주파 신호 시뮬레이터<sup>[2]</sup>, 적외선 신호 시뮬레이터<sup>[2]</sup> 등 다양한 표적 신호 모의 장비들이 활용된다. HWIL 시뮬레이션 제어 시스템은 HWIL 시뮬레이션의 핵심시스템으로 유도탄 운동과 관련된 소프트웨어 모델을 실시간으로 연산하고, HWIL 시뮬레이션 시험장비, 유도탄 부체계와의 실시간 자료 입/출력을 수행하며, 결과 분석을 위해 시뮬레이션 자료를 실시간으로 획득하는 핵심적인 기능을 가져야 한다.

HWIL 시뮬레이션 제어 시스템과 관련된 연구로 초고주파 시뮬레이션 시스템<sup>[11]</sup>을 활용한 실시간 제어 시스템 개발<sup>31</sup>, AMRDEC의 PC 기반 초고주파 시뮬레이션 시스템 제어 시스템<sup>[4]</sup>, HWIL 시뮬레이션 자료를 가시화하는 시스템<sup>[5]</sup> 등 다양한 종류의 HWIL 시뮬레이션 시스템들이 구현되고 있다. 그러나 이러한 시스템들을 고기동 유도탄의 HWIL 시뮬레이션에 그대로 적용하기는 어렵고, 유도탄의 특성에 맞는 HWIL 시뮬레이션 제어 시스템을 개발하여야 한다.

### Ⅲ. HWIL 시뮬레이션 제어 시스템 개발 기법

이 장에서는 고기동 유도탄의 HWIL 시뮬레이션을 위한 제어 시스템의 하드웨어 구성 및 소프트웨어 개 발 기법을 제시한다.

### 3.1 HWIL 시뮬레이션 제어 시스템 하드웨어

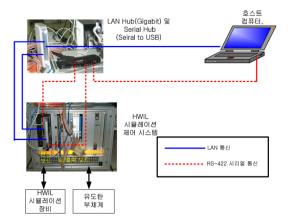

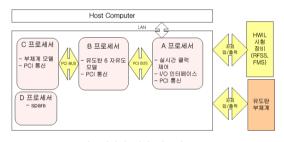

일반적으로 고기동 유도탄의 소프트웨어 시뮬레이션 모델은 복잡한 연산을 수행하고 짧은 적분주기를 갖는다. 따라서 HWIL 시뮬레이션 제어 시스템은 실시간 연산과 자료 입/출력을 위해 다수의 연산보드들을 탑재하여 병렬처리가 가능한 고성능의 연산보드를 사용하는 것이 바람직하다. 또한 자료 입/출력에 소요되는 시간을 최소화하기 위해 그림 2와 같이 VME 버스를 사용하여 연산보드와 다양한 입/출력 보드들을 함께 탑재하고, 프로그램을 다운로드하여 제어하는 임베디드 시스템으로 구축하는 것이 유리하다. 그림 2는 LAN과 RS-232를 이용하여 호스트 컴퓨터로부터 부트 이미지, HWIL 시뮬레이션 프로그램을 VME 버스시스템으로 다운로드하고 HWIL 시뮬레이션을 제어하는 임베디드 시스템으로 다운로드하고 HWIL 시뮬레이션을 제어하는 임베디드 시스템이다.

본 논문에서는 한 개의 보드에 1.25GHz POWER PC CPU를 4개(A, B, C, D 프로세서) 장착하고, 각각의 CPU 마다 256 MBytes의 독립된 메모리를 가지며, PCI 버스로 프로세서 통신이 가능한 CHAMP AV

그림 2. 하드웨어 구성

IV<sup>[6]</sup>연산 보드를 사용하는 방식을 제안하였다. 일반적으로 CPU의 갯수는 CPU의 연산 성능, 유도탄 6자유도 비행운동 모델의 복잡도, 적분주기, I/O 인터페이스 복잡도를 종합적으로 고려하여 결정된다. 제시된시스템은 고기동의 유도탄 6자유도 비행운동 모델 연산을 수행하고, 다양한 I/O 인터페이스를 수행함을 고려하여 고성능의 연산 프로세서 사양을 선택하였다. 입/출력 보드는 유도탄 부체계 인터페이스와 HWIL시뮬레이션 시험장비 인터페이스를 고려하여 Reflective Memory(RM), RS-422, 1553B, 아날로그입/출력 보드들을 탑재하였다.

## 3.2 HWIL 시뮬레이션 제어 시스템 소프트웨어

HWIL 시뮬레이션 제어 시스템은 고기동 유도탄 6자유도 비행운동 모델의 안정적인 해를 구할 수 있는 실시간 연산, 다양한 I/O 인터페이스, 자료 획득기능을 제공해야 한다. 따라서 HWIL 시뮬레이션 제어 시스템 소프트웨어는 실시간 연산을 위해 복잡한모델을 분산하여 처리하기 위한 업무 할당기법, 프로세서를 실시간으로 제어하는 기법, 분산된 프로세서사이의 실시간 통신 기법, 자료 분석을 위해 시뮬레이션 자료를 실시간으로 획득하는 기법을 지원해야한다.

#### 3.2.1 HWIL 시뮬레이션 업무 할당 알고리즘

적분주기가 작은 고기동 유도탄 6자유도 비행운동 모델을 실시간으로 연산하고 복잡한 하드웨어 인터페 이스를 수행하는 시스템을 한 개의 프로세서로 구현 하는 것은 쉽지 않다. 따라서 여러 개의 프로세서에 업무를 분산하는 기법을 사용해야한다. 이 장에서는 n 개의 연산 보드 가운데 n-1개의 프로세서를 사용하여 태스크를 할당하는 기법(알고리즘1)을 제시한다. 제시

알고리즘 1. 프로세서 업무 할당 알고리즘

```

no_of_used_processor = 1:

for (j < no_of_subsystem) {

if (no\_of\_used\_processor) (no\_of\_processor)) {

Simplify_the_Whole_Models(): /* 프로그램재구성*/

/* 전체의 FrameTime */

\sum_{i \neq Allocated\_other\_processor}^{n}

T_{Model_i} + T_{AirFrame})

> Step_time) {

Search_Max_T_Model_k();

/* Model을 제외한 나머지 FrameTime) */

\text{if } (\sum_{i \neq Model_k}^n T_{Model_i} + \ T_{Air\_Frame} \ \langle \texttt{Step\_time}) \{ -- \ \textcircled{2} \}

/*Task로 할당 */

I_{model}/Step\_time

\sum

(Step\_time - Frame\_Time_n)

\langle T_{\text{mod}el_{l}} \rangle

Separete_Model_k();

Make_it_a_Task();

continue;

Separete_Model_k();

Assign_it_to_Processor_i();

if ( T_{Model_k} > I_{Model_k}) ----

Simplify_the_Model_k();

no_of_used_processor ++

} else break;

```

된 기법은 실시간 시뮬레이션을 위한 프로그램 연산시간(Frame\_Time)이 적분주기(Step\_Time) 보다 작도록 설계하는데 목적이 있으며, HWIL 시뮬레이션을 수행하기 전에 사용될 수 있다. I/O 인터페이스 업무가 유도탄 6자유도 비행운동 모델을 연산하는 시간에 영향을 줄 수 있으므로 한 개의 프로세서는 I/O 인터페이스를 위한 전용 프로세서로 지정하였다.

연산시간이 적분주기보다 크다면(①) 각 부체계 모델의 연산시간( $T_{Model_t}$ )을 비교하여 가장 큰 모델을 분리한 후, 해당 부체계 모델이 제외된 상태에서 실시간으로 수행 가능한지 판단한다(②). 실시간 연산이 가능하면 분리된 모델을 멀티태스킹을 사용하여 계산이가능한지 확인(③)한 후, 불가능한 경우에 한하여 독립된 프로세서를 이용한 병렬 처리를 수행한다. 병렬처리를 수행할 때 분리된 모델의 연산시간( $T_{Model_t}$ )이모델의 연산주기(( $I_{Model_t}$ ) 보다 클 경우(④)에는 부체계 모델을 재설계하여 간략화해야 한다. 이러한 최적화 작업은 모든 부체계 모델을 포함한 유도탄 6자유도 비행운동 모델이 적분주기 내에 계산될 때까지 수행한다. 다중 태스크가 한 개의 프로세서에서 연산되는 멀티태스킹을 사용할 때(③)에는 선점형 우선순위스케쥴링을 사용한다.

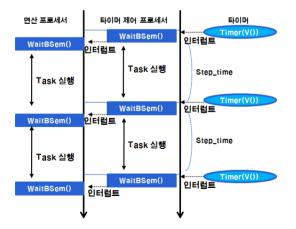

### 3.2.2 실시간 타이머 제어 및 실시간 연산 기법

고기동의 HWIL 시뮬레이션은 작은 적분주기를 갖는 연속 시간 시뮬레이션으로 수행되고, 시뮬레이션 시간이 실제 시간 흐름에 동기화되어 동작해야 한다. 또한 I/O를 수행하는 프로세서와 유도탄 6자유도 비행운동 모델을 연산하는 각 프로세서들은 시간이 동기화되어야 안정적인 제어루프를 형성할 수 있다. 앞절에서 제시한 알고리즘에 의해 업무들이 프로세서에할당되면, 각 프로세서들은 정해진 적분주기로 타이머에 동기화되어 동작하여야 한다. 여러 프로세서들의시간 동기화를 위해 그림 3의 기법을 고안하였다.

여러 프로세서 가운데 한 개의 프로세서를 타이머 제어 프로세서로 선택하고 CPU 클럭의 타이머 인터 럽트가 발생하면 타이머 제어 프로세서의 이진 세마 포어에서 대기(WaitBSem())하는 프로세서의 태스크를 활성화시킨다. 활성화된 프로세서는 인터럽트를 이용하여 다른 프로세서의 이진 세마포어에서 대기하는 태스크를 활성화시킨다. 각 프로세서에서 활성화된 태스크들은 할당된 업무를 수행하고 세마포어에서 다음 활성화 명령을 기다린다.

유도탄의 6자유도 비행운동 모델을 계산하기 위해서는 연속 동특성 모델의 미분방정식 및 대수 방정식을 연산하고 독립변수인 시간에 대한 적분을 수행하여야 한다. HWIL 시뮬레이션에서는 시간 제약성이중요하기 때문에 식(1)과 같은 적분식을 갖는 AB2 (Adams-Bashforth 2nd order) 방식<sup>[7]</sup>을 사용한다.

$$y_{n+1} = y_n + \frac{h}{2}(3f_n - f_{n-1})$$

(1)

$y_n$ : 시간  $T$ 에서의 상태변수

$h$ : 적분간격

$f_n$ : 미분방정식

그림 3. 실시간 타이머 제어 기법

### 3.2.3 프로세서 실시간 자료 통신

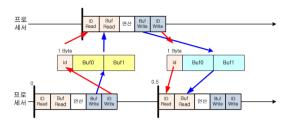

일반적으로 프로세서 사이의 실행 동기화를 위해서는 파이프, 메시지 큐와 같은 프로세서 동기화 기법을 사용한다. 이 논문에서는 컴퓨터 네트워크에서 사용하는 동기식, 비동기식 통신 방식을 응용하여 타이머와 1 바이트 공유 메모리를 사용하여 통신 자료의 무결성을 만족시키는 프로세서 통신 방법 두 가지를 제시하다

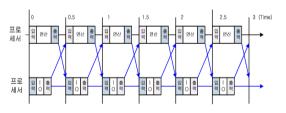

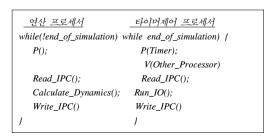

첫 번째는 알고리즘 2와 같은 의사코드를 갖고 그림 4와 같이 동작하는 동기식 통신 방법이다. 타이머에 의해 활성화된 프로세서가 V() 명령을 사용하여다른 프로세서를 활성화시킨 후, 다른 프로세서로부터전송된 자료를 읽는다(Read\_IPC()). 자료를 읽은 프로세서는 입력된 자료를 사용하여 할당된 연산을 수행한 후, 수행 결과를 다른 프로세서에 전송(Write\_IPC())한다. P()에서 대기하는 나머지 프로세서들도 같은 방식으로 동작하면 그림4와 같이 출력결과가 다음 프레임에 다른 프로세서로 입력되므로임계섹션(Critical Section) 문제가 발생하지 않는다.

동기식 통신 방식은 유도탄 부체계나 HWIL 시뮬레이션 장비 제어를 위한 제어 명령을 입/출력 전담프로세서로 빠르게 전달할 목적으로 사용되었다. 이방식은 다수의 프로세서가 동기화되어 동작하는 환경에서 무결점의 통신을 제공할 수 있다.

두 번째는 그림 5와 같이 동작하는 비 동기식 통신 방법이다. 한 바이트의 임계섹션에 동시에 접근하여도 자료의 무결성이 보장된다는 가정 하에 통신하는 두

그림 4. 동기식 통신 기법

알고리즘 2. 프로세서 동기화 및 통신 기법

그림 5. 비동기식 통신 기법

프로세서 사이에 경쟁 조건(Race condition)을 허용한 더블 버퍼를 사용하였다. 그림 5와 같이 프로세서 사이에 두 개의 버퍼(Buf0와 Buf1)와 1 바이트 "ID" 플래그를 할당한 후, "ID" 필드가 지정하는 않는 버퍼에 자료를 갱신하고 갱신한 버퍼 번호를 "ID" 필드에 마지막으로 지정하는 방식이다. 상대 프로세서가 자료를 읽을 때는 "ID" 필드가 지정한 버퍼의 자료를 읽는다. 이와 같은 방식을 사용하면 읽기와 쓰기 작업의 충돌을 방지하면서 가장 최근에 갱신된 버퍼의 자료를 읽을 수 있다. 비동기식 통신 방법은 업무할당 알고리즘에 의해 여러 개의 프로세서로 분산되어 서로 다른 주기로 계산되는 부체계 모델들의 자료 통신에 사용된다. 이 방법은 한 개의 출력 프로세서와 다수의 입력 프로세서가 공존하는 환경에서 입/출력에 소요되는 시간이 적부주기보다 작은 경우 유효하게 동작한다.

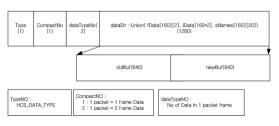

# 3.2.4 실시간 자료 획득 기법

HWIL 시뮬레이션 제어 시스템은 실시간으로 동작하기 위해 통신에 소요되는 시간을 줄여야 하므로 UDP/IP를 사용하는 자료 획득 프로토콜을 설계하였다. IEEE802.3<sup>[8]</sup>의 PDU가 1500바이트임과 UDP/IP 패킷 헤더 크기 28바이트임<sup>[8]</sup>을 고려하여 1280바이트 PDU를 갖는 그림 6과 같은 패킷 구조를 설계하였다.이 패킷에는 각각 160 채널을 갖는 연속된 1 프레임의 자료가 포함될 수 있다.

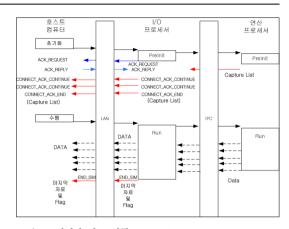

실제 자료 통신을 위한 프로토콜은 그림 7과 같이 초 기화 단계와 시험 단계로 구분하여 설계하였다. 초기화 단계에서는 "ACK REOUEST" 패킷과 "ACK REPLY"

그림 6. 패킷 구조

그림 7. 실시간 자료 획득 프로토콜

패킷을 이용한 2단계 연결과정(2-way handshake)을 거쳐 호스트 컴퓨터와 연결 설정을 수행한다. 연결 실패시 일정한 시간동안 대기한 후 동일한 연결 설정을 반복하며, 최대 3회까지 시도한다. 연결이 설정되면 "CONNECT\_ACK\_CONTINUE"와 "CONNECT\_ACK\_END" 패킷을 사용하여 획득될 자료에 대한 정보(채널 개수, 각 채널 자료의 이름)를 획득한다. 시뮬레이션 수행 단계에서는 시뮬레이션 자료가 "DATA" 패킷에 패킹되어 1KHz 주기로 호스트 컴퓨터에게 전송된다.

# Ⅳ. HWIL 시뮬레이션 제어 시스템 개발 결과

이 장에서는 HWIL 시뮬레이션 제어 시스템 개발 결과로 구현 내용과 성능을 소개한다.

#### 4.1 HWIL시뮬레이션 제어 시스템 구현

프로세서 4개(A,B,C,D 프로세서)가 탑재된 CHAMP AV IV 보드<sup>[6]</sup>를 사용하여 HWIL 시뮬레이션 제어 시스템을 개발하였다. 운영체제는 실시간 제어를 수행해야 하는 점을 고려하여 상용의 실시간 운영체제인 VxWorks<sup>[9]</sup>를 선택하였다. 적분주기는 적용대상 고기동 유도탄 6자유도 비행운동 모델의 해를 안정적으로 구할 수 있고, HWIL 시뮬레이션 제어 시스템의 연산 성능을 만족할 수 있는 0.5msec를 선택하였다.

적용대상 고기동 유도무기체계는 각 부체계 모델들이 서로 다른 고유의 연산주기와 계산시간을 가지지만한 개의 부체계 모델을 제외한 다른 모델들은 적분주기내에 연산이 가능했고 한 개의 부체계 모델의 연산 시간( $Model_{frame\ time}$ )이 적분간격  $< Model_{frame\ time}$

연산주기 조건을 가졌다. 업무들을 각 프로세서에 할 당하기 위해 알고리즘1에 사용하여 최적의 프로세서 할당 방법을 분석하였고, 그 결과를 바탕으로 I/O 프로세서, 위의 부체계 모델, 유도탄 6자유도 비행운동모델을 각각의 독립된 프로세서에 할당하였다.

그림 8은 프로세서에 업무를 할당한 결과를 보여준다. 각 프로세서는 유도탄 6자유도 비행운동 모델 연산, 프로세서 사이의 실시간 통신, I/O 인터페이스를 수행하도록 구성되어 있다. A 프로세서에는 특별히전체 시스템의 실시간 클럭을 통제하는 기능과 유도탄 부체계 및 HWIL 시뮬레이션 시설과의 인터페이스업무를 총괄하도록 구현하였다. 이와 같은 환경에서 A 프로세서와 B 프로세서는 같은 실행주기로 동작하고, 동기식 통신 방법을 사용하여 자료 통신이 이루어지도록 구현하였다. 서로 다른 실행 주기를 갖는 B 프로세서와 C 프로세서는 서로 다른 실행주기로 동작하며, 비동기식 통신 방법을 사용하여 통신이 이루어지도록 구현하였다.

그림 8. HWIL 시뮬레이션 제어 시스템

#### 4.2 HWIL시뮬레이션 제어 시스템 성능

개발된 HWIL 시뮬레이션 제어 시스템의 성능은 적분주기 내에 실시간 연산이 종료되는지 여부, 예측 된 시간지연을 만족하며 무결점 자료 통신을 수행하 는지 여부, 패킷의 손실율을 측정하여 검증하였다.

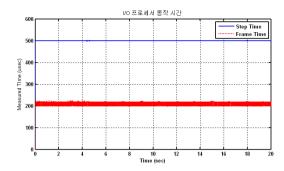

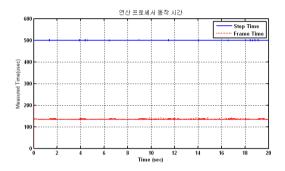

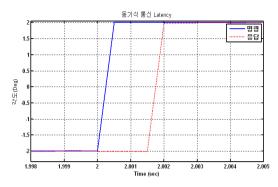

그림 9, 그림 10은 프로세서들의 실제 연산 시간 (FrameTime)과 적분주기(Step\_Time)를 측정한 결과이다. 한 개의 프로세서에서 연산한 경우 0.5+  $Model_{frame\_time}$ 의 연산 시간이 소요될 것으로 예상되지만 멀티 프로세싱을 이용함으로써 연산 프로세서와 자료 입/출력 프로세서의 동작 주기가 적분주기인 0.5msec를 만족함을 확인할 수 있다.

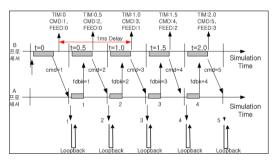

동기식 및 비동기식 통신의 성능은 루프백 테스트를 통해 확인하였다. 그림11 과 같이 루프백 시간 지연이 없는 환경에서 2.3절의 동기식 통신 기법을 사용할 때 연산 프로세서에서 출력된 명령값(cmd)은 I/O

그림 9. 입/출력 프로세서 수행 시간

그림 10. 연산 프로세서 수행 시간

그림 11. 통신 지연 시간 예측

프로세서를 거쳐 1msec 후에 수신된다. 즉, t=0에서 송신된 명령값(cmd=1)은 1msec 후인 t=1.0에서 수신 되게 된다. 시뮬레이션 시간(t)이 0.0 ~ 2.0으로 진행되고 명령값(cmd)이 1~5까지 증가한다면 피드백되는 값도 1msec 지연되어 연속적으로 수신된다. 그림 11은 최소의 시간이 지연이 발생할 때의 시간 지연 예측값이고, 그림 12는 실제 측정한 아날로그 통신 지연 값이다. 아날로그 보드 제어 시간 때문에 예측값보다한 프레임 추가된 1.5msec의 시간지연이 발생하였다.

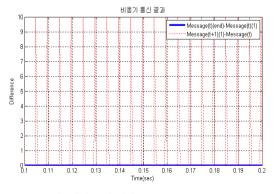

비동기식 통신의 성능을 측정하기 위한 환경은 적 분주기 0.5msec(B 프로세서)와 연산주기 5msec(C 프 로세서)로 동작하는 두 개의 프로세서를 사용하여 구

그림 12. 아날로그 통신 시간 지연

현하였다. B 프로세서에서 시간이 증가할 때마다 선형으로 증가하는 값을 32 워드 메시지(Message(t) 1:32))에 동일하게 복사한 후 C 프로세서로 송신하였다. C 프로세서는 수신된 메시지를 5msec마다 B 프로세서로 피드백하였다. 그림 13의 실선은 한 메시지내의 첫 워드와 마지막 워드의 차이를 비교한 그림으로 동일한 워드값(차이가 0)을 수신함으로써 자료의무결성을 보장함을 알 수 있다. 점선은 Message(t)(0)-Message(t-1)(0)를 도시한 그림으로 5ms마다 일정하게 10의 차이가 발생함으로 실시간 통신이 정확하게수행됨을 확인할 수 있다.

실시간 자료 획득 프로그램은 1326 바이트(패킷 PDU(1284바이트)+패킷 헤더(42 바이트))를 1KHz 주기로 전송하도록 설계되었기 때문에 10,608 Kbps의대역폭이 필요하다. 기가비트 이더넷 환경에서 자료를 획득하여 자료의 개수 와 Message(t)(0)- Message (t-1)(0)를 측정하였다. 20초의 시뮬레이션 주기 동안 40001개의 자료를 획득하였고, 그림13과 같이 일정한차이가 발생함을 확인함으로써 통신에 의한 자료 손실이 없음을 확인하였다.

그림 13. 비동기식 통신 결과

# V. 결 론

본 논문에서는 고기동 유도탄 HWIL 시뮬레이션 제어 시스템 개발에 사용될 수 있는 프로세서 업무 할당 알고리즘, 타이머 제어 기법, 프로세서 실시간 자료 통신 기법 및 실시간 자료 획득 기법을 제안하였다. 제시된 기법들은 빠른 적분주기를 갖는 유도탄 6자유도 비행운동 모델 및 부체계 모델들을 HWIL 시뮬레이션 적분주기 내에 연산하는 것을 목표로 개발되었으며, 여러 프로세서에 업무를 할당하는 방법, 적분주기에 따라 타이머를 제어하는 기능, 프로세서 사이의 실시간 자료 전송 기능, 시뮬레이션 수행 중에 생성되는 시뮬레이션 자료들을 실시간으로 획득하는 기능을 제공한다.

본 논문에서 제안한 기법은 4개의 프로세서를 갖는 연산 보드를 기반으로 구현되었고, 시뮬레이션 적분주기 측정과 루프백 테스트를 수행한 후 I/O 인터페이스의 시간 지연 및 송수신 자료를 비교함으로써 성능을 검증하였다. 개발된 시스템은 고기동의 유도탄 HWIL 시뮬레이션에 성공적으로 활용되었다.

본 논문에서 제시된 기법들은 HWIL 시뮬레이션 시스템을 구현하는데 보편적으로 이용될 수 있지만 특정 플랫폼에서 동작하도록 구현된 한계가 있다. 따라서 제시된 기법들을 사용하여 HWIL 제어 시스템을 구현할 때 개발 플랫폼의 영향을 적게 받을 수 있도록 이식성을 향상시키는 연구가 추가적으로 수행되어야 한다.

## 참 고 문 헌

- [1] 김영주, 곽병철, 이기오, 김진형 "마이크로파 호 밍 유도무기 HILS를 위한 RFSS 개발", *국방기* 술연구, pp.203-212, 2004

- [2] M. D. Trotsky, "PAC-3 Missile Ground Testing for Success in Flight," *The First Annual International Missiles and Rockets Symposium* and Exhibition, February 2000.

- [3] 김기승, 김영주, 홍정운, "HWIL 시뮬레이션을 위한 통합 제어 시스템 고찰," *대한 전기학회 하 계학술대회 논문집*, pp2659-2661, July 2002.

- [4] D. Beck, R. Bennett, "Implementation of a Personal Computer Based Real-Time Hardware-in-the-Loop U.S Army Aviation and Missile Command Simulator," Proc. SPIE Vol.4717, pp.24-31, 2002.

- [5] J. A. Buford Jr., T. A. Garcia, M. H. Bowden, "Re-configurable visualization for HWIL simulation," *Proc. SPIE Vol.3367*, pp.122-128, August 1998.

- [6] CHANPTools Software User's Manual, Curtiss-wright controls embedded computing, May 2006.

- [7] S. D. Conte, C. D. Boor, *Elementary numerical analysis: An algorithmic approach*, McGraw-Hill, 1980.

- [8] W. R. Stevens, TCP/IP Illustrated, Volume I: The Protocols, Addison Wesley, 1994.

- [9] *VxWorks programmer's guide 5.5*, Windriver system inc, July 2002.

이 병 선 (ByungSun Lee)

정회원

2004년 2월 중앙대학교 전기 전자제어공학부2006년 2월 연세대학교 전기 전자공학과 석사

2006년 1월~현재 국방과학연 구소

<관심분야> HWIL 시뮬레이션,

통신공학, 초고주파 환경구현

김 운 식 (WoonSik Kim)

Kim) 정회원 1994년 2월 충남대학교 전산 학과

1996년 2월 충남대학교 전산 학과 석사

1996년 3월~현재 국방과학연 구소

2007년 3월~현재 충남대학교 컴퓨터공학과 박사과정

<관심분야> HWIL 시뮬레이션, 분산 시뮬레이션, Wireless Sensor Networks 김 상 하 (SangHa Kim)

종신회원

1980년 서울대학교 학사 1984년 University of Houston 석사

1989년 University of Houston 박사

1992년~현재 충남대학교 전기 정보통신공학부 교수

<관심분야 Internet Routing, Wireless Sensor Networks, MANET, 4G, Mobility, Multicast 등