#### 논문 17-42-09-01

# 기준전압 가변 비교기와 스텝당 2비트 기법을 이용한 10비트 축차비교 레지스터 A/D 변환기 설계

이 상 헌<sup>\*</sup>, 이 호 용<sup>\*</sup>, 윤 광 섭<sup>°</sup>

# Design of a 10Bit Comparison Register A/D Converter with 2Bit/Step and Threshold Configuring Comparator

Sang-Heon Lee\*, Ho-Yong Lee\*, Kwang-Sub Yoon

요 약

본 논문은 기준전압 가변 비교기와 스텝당 2비트 기법을 이용한 10비트 SAR(successive approximation register) A/D 변환기를 제안한다. 전체 회로 구조는 상위5비트를 위한 기준전압 가변 비교기, 하위5비트 커패시터 D/A 변환기로 구성되어서 축전기 개수, 전력소모를 감소시켰다. 클럭 주기를 반감시키는 클럭 두배 회로를 이용해 스텝당 2비트를 결정해서 변환속도를 증가시켰다. 제안하는 A/D 변환기는  $0.18\mu m$  CMOS 공정을 이용하여 제작하였고 10MS/s의 변환속도를 갖는다. 9.5비트의 ENOB(effective number of bit)이 측정되었고, INL / DNL은 각각  $\pm 1$  / 0.5LSB이고, 칩 면적과 전력소모는 각각  $750x700\mu m^2$ 와  $56\mu W$ 이고, 50M은 50M

Key Words: SAR ADC, Threshold Configuring Comparator, 2bit/step

#### **ABSTRACT**

This paper proposed a 10 bir SAR A/D converter with 2bit/step and Threshold Configuring Comparator. The structure of the entire circuit is composed of a Threshold Configuring Comparator for the 5MSBs and a 5LSBs capacitor D/A converter, reducing the number of capacitors and power consumption. By using a clock doubling circuit that halves the clock cycle, 2 bits were determined for each step to increase the conversion speed. The proposed A/D converter is fabricated using a  $0.18\mu m$  CMOS process and has a conversion speed of 10 MS/s. A 9.5 bit ENOB(effective number of bit) is measured, INL / DNL are  $\pm 1$  / 0.5LSB, chip area and power consumption are  $750x700\mu m^2$  and  $56\mu W$  respectively, and FoM has 7.73fJ/step.

## I. 서 론

회로설계의 집적화 및 공정기술의 발전은 정보통신 기기의 소형화, 저 전력화를 통해서 정보통신 산업을 발전 시켰다. 이러한 이유로 기기의 소형화가 가속되고 있다. 최근에는 저 전력의 설계가 가능한 SAR(successive approximation register) A/D 변환기에 대한 연구가 많이 진행되고 있다<sup>[1-4,7-10]</sup>.

<sup>※</sup> 본 연구는 미래창조과학부 및 정보통신기술진흥센터의 대학ICT연구센터육성 지원사업의 연구결과로 수행되었음 (IITP-2017-2012-0-00641)

<sup>※</sup> 본 논문은 2015년도 정부(교육부)의 재원으로 한국연구재단의 지원을 받아 수행된 기초연구사업임. (2015RIB1A1A01058603)

<sup>※</sup> 반도체설계교육센터(IDEC)의 CAD Tool 지원에 감사드립니다.

<sup>•</sup> First Author: Inha University Department of Electronic Engineering, lsh6032@naver.com, 학생회원

<sup>°</sup> Corresponding Author: Inha University Department of electronic Engineering, ksyoon@inha.ac.kr, 종신회원

<sup>\*</sup> Inha University Department of electronic Engineering, ghdyd1801@naver.com 논문번호: KICS2016-12-379, Received December 12, 2016; Revised June 2, 2017; Accepted September 14, 2017

SAR A/D 변환기는 다중 스텝을 통해서 데이터가 변환이 되어서 변환속도에 한계가 있다. 이러한 단점을 보완하기 위해 스텝당 2비트 이상의 변환을 통해서 변환속도를 증가시키는 방법이 이용된다<sup>[1-4]</sup>. 그러나 커패시터 D/A 변환기의 증가와 부가적인 회로에의해 전력소모가 증가하게 된다<sup>[1-2]</sup>.

제안하는 회로는 기준전압 가변 비교기와 스텝당 2 비트 기법을 이용해서 SAR A/D 변환기의 속도를 향상시키고 전력소모를 감소시켰다. 제안하는 구조는 분할방식을 적용하여, 상위5비트 변환 시에는 기준전압 가변 비교기를 이용하고 하위5비트 변환에는 기존의 SAR A/D 변환기의 커패시터 D/A 변환기의 스위칭을 통해서 데이터를 변환한다. 상위5비트에 기준전압가면 비교기를 적용하여 커패시터 D/A 변환기의 커패시터 개수를 줄여서 칩 면적과 동적 전력소모를 감소시킨다.

2장에서는 구현된 10비트 SAR A/D 변환기의 구조와 동작원리, 그리고 구성 회로들을 구체적으로 설명한다. 3장에서는 제안하는 A/D 변환기의 시뮬레이션 결과, 4장에서는 결론을 맺는다.

### Ⅱ. 제안하는 SAR A/D 변환기

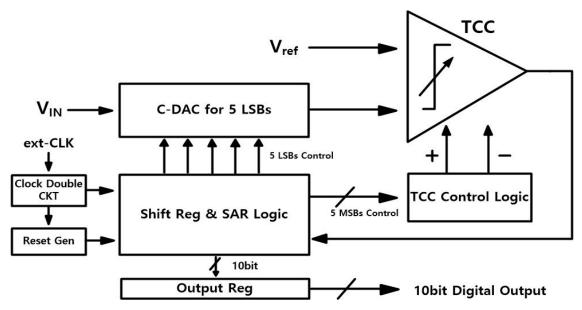

그림 1은 제안하는 10비트 SAR A/D 변환기의 전체 블록도이다. 전체 블록은 상위5비트 변환 시 오프 셋을 가변시키는 기준전압 가변 비교기와 입력신호를

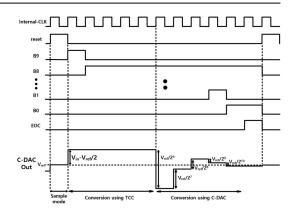

그림 2. 제안된 SAR A/D 변환기의 타이밍도와 C-DAC의 출력파형 Fig. 2. The timing diagram of proposed SAR A/D Converter and output waveform of C-DAC

샘플링하고 하위5비트 변환 시 기준전압을 생성하는 커패시터 D/A 변환기로 구성된다. 기준전압 가변 비교기 제어 회로, 스위치 제어회로, SAR 논리회로, 출력단, 그리고 클럭 더블 회로로 이루어져 있다. 기존의 스텝당 2비트 SAR A/D 변환기에서 한 개의 비교기와 커패시터 D/A 변환기를 사용하여 전력소모를 최소화한다.

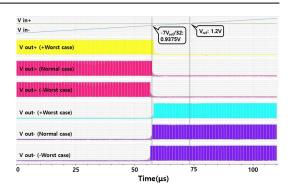

설계된 SAR A/D 변환기의 클럭 타이밍도와 커패 시터 D/A 변환기의 출력 파형은 그림 2와 같다. 클럭 더블 회로에 의해 외부 클럭의 주기가 반감되어 내부 클럭이 생성되고, 리셋 파형이 발생한다. 리셋 신호에

그림 1. 제안된 SAR A/D 변환기 Fig. 1. Proposed SAR A/D Converter

서 입력 신호가 하위5비트를 위한 커패시터 D/A 변환기에 의해 샘플링되어  $\frac{Vref}{2}$  와 입력신호를 비교하여 MSB(most significant bit)를 결정한다. MSB가 1이면 기준전압 가변 비교기의 오프셋을  $-\frac{Vref}{4}$  만큼 변화시키고, MSB가 0이면 기준전압 가변 비교기의 오프셋을 +  $\frac{Vref}{4}$  만큼 변화시켜서 두 번째 MSB를 결정한다. 이와 같이 5번째 MSB를 결정할 동안 오프셋을  $\frac{Vref}{2^N}$  만큼 증감시켜서 데이터를 변환한다. 이 결과, 그림 2의 커패시터 D/A 변환기의 출력파형은 상위5비트동안 일정하여 동적 전력소모를 줄일 수 있다. 상위5비트 데이터 변환이 완료되면 기준전압 가변 비교기의 오프셋을 변화시키지 않고 기존의 SAR A/D 변환기와 같이 커패시터 D/A 변환기의 스위칭을 이용하여 기준전압을 변화시켜서 하위5비트를 결정한다.

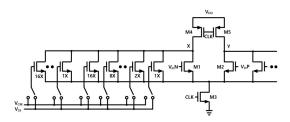

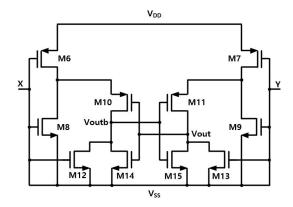

그림 3, 4는 각각 기준전압 가변 비교기의 첫 번째 단과 래치 단을 보여준다. 비교기의 오프셋을 제거하 기 위해서 비교기의 오프셋을 가변시키는 비교기가 이용되어왔다<sup>[3,7]</sup>. 제안하는 A/D 변환기에 이용된 기

그림 3. 기준전압 가변 비교기의 첫 번째 단 Fig. 3. The first stage of Threshold Configuring Comparator

그림 4. 기준전압 가변 비교기의 래치 단 Fig. 4. The latch stage of Threshold Configuring Comparator

준 전압 가변 비교기는 입력 쌍에 전류 패스를 두어 오프셋을 가변 시키는 구조가 사용되었다<sup>[3]</sup>. CLK이 '0'이 되면 노드 X, Y가 풀업이 되어서 리셋모드가 된다. CLK이 '1'이면 노드 X, Y의 전압이 풀다운 되 는데, 입력 전압의 차이에 의해 전압 하강 시간이 달 라진다. 이 차이를 래치 단이 증폭하여 디지털 출력을 생성한다. 기준전압 가변 비교기의 가변 스위칭 과정 에서의 선형성은 리셋 모드와 비교 모드에서 시간 여 유를 두어서 보장하였다.

비교기의 오프셋은 전류패스를 온/오프 시켜서 전압 하강 시간을 변화시켜서 변화시킨다. 기준전압 가변 비교기는 공정 오차에 의해 오프셋 오차가 발생하게 되어서 하위비트 결정 시 데이터 오류가 발생한다. 따라서 제안하는 구조는 상위5비트에 기준전압 가변비교기를 사용하여 오차를 최소화하였다.

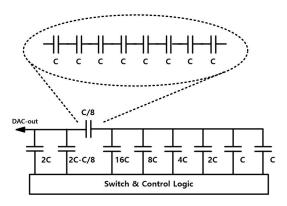

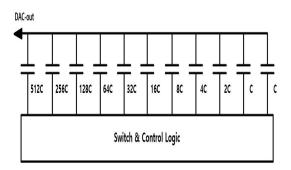

제안하는 구조의 하위5비트를 위한 커패시터 D/A 변환기의 회로도는 그림 5와 같다. 2C, 2C-C/8은 A/D 변환기의 입력신호를 샘플링하기 위해서 사용된다. 8 개의 C는 직렬로 연결되어서 하위5비트 배율을 맞추 기 위해서 사용되고, C부터 16C는 하위비트의 기준전 압 생성을 위해 사용된다. 제안하는 커패시터 D/A 변 환기는 그림 6과 같이 일반적인 10비트 변환기의 커 패시터 개수보다 적게 사용된다. 일반적인 경우,  $2^{10}$ =1024개의 커패시터가 사용되지만, 제안하는 구조는 44개의 커패시터를 사용하여 약 4.3%의 감소를 보인 다. SAR A/D 변환기에서 많은 전력 소모를 차지하는 커패시터 D/A 변환기의 커패시터 개수를 줄여서 동적 전력 소모를 줄이고, CMOS 공정에서 많은 면적을 차 지하는 커패시터에 의해 칩 면적도 감소시킬 수 있다. 제안하는 커패시터 D/A 변환기에 이용된 단위 커패시 터는 502.8fF이다. 직렬의 커패시터 연결은 common centroid 기법을 활용하여 기생 성분을 최소화하였다.

그림 5. 하위5비트를 위한 커페시터 D/A 변환기 Fig. 5. The capacitor D/A converter for 5LSBs

그림 6. 일반적인 커패시터 D/A 변환기

Fig. 6. The conventional capacitor D/A converter

그림 7. 클럭 더블 회로 Fig. 7. The block diagram of clock double circuit

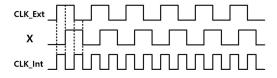

클릭 더블 회로의 블록도는 그림 7과 같다. 배타적 논리회로와 지연 셀을 이용하여 입력된 클럭의 주기를 반감시킨다. 이 결과, 외부 클럭의 주파수가 두 배가 되는 내부 클럭이 생성되어서 스텝당 2비트 디지털 코드를 결정된다. PVT 변화가 발생하면, TCC의가변 스위칭 과정에서 시간 여유가 없어져서 정확성이 낮아져서 정확한 데이터 변환이 가능하지 않다. 본논문에서는 PVT변화를 고려하지 않고 시뮬레이션을 진행하였다.

#### Ⅲ. 실험 결과 및 고찰

그림 8에서는 기준전압 가변 비교기의 몬테카를로 시뮬레이션 결과이다. 시뮬레이션은 상위5비트가 '10111'일 때(오프셋변화:  $-\frac{7 \, Vref}{32}$ )의 결과이다. 몬테카를로 시뮬레이션은 공정오차와 소자 부정합 오차를 모두 고려한 시뮬레이션이다. 오프셋이  $\frac{7 \, Vref}{32}$ 만큼 줄어들어서 기준전압이 1.2V에서 0.9375V로 변화되었는데 시뮬레이션 결과에서는 약±16mV의 오차가 발생되었다. 이러한 이유로 제안하는 구조는 상위5비

그림 8. 기준전압 가변 비교기의 몬테카를로 시뮬레이션 Fig. 8. The Monte-Carlo simulation of Threshold Configuring Comparator

트에서 기준전압 가변 비교기를 사용하였다.

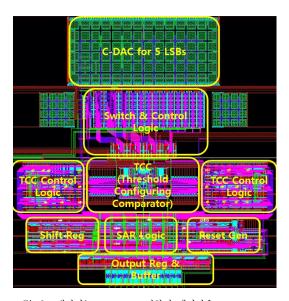

제안하는 A/D 변환기는 0.18 $\mu$ m CMOS 공정을 사용하여 제작되었고, 그림 9는 A/D 변환기의 레이아웃 사진이며 전체 칩 면적은 750x700 $\mu$ m²이다. 레이아웃 상단에는 아날로그 블록인 커패시터 D/A 변환기와 스위치를 배치하였고, 중앙에는 기준전압 가변 비교기를, 양단에는 기준전아 가변 비교기의 제어 논리회로가 있다. 하단에는 SAR 논리회로, 리셋 파형 생성기, 시프트 레지스터, 그리고 출력단과 버퍼로 이루어져있다.

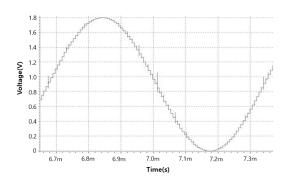

제안하는 SAR A/D 변환기의 공급전압은 1.8V이며, 기준전압은 1.2V이다. 10MS/s의 샘플링 주파수, 1.5kHz의 아날로그 정현파 입력신호에 대해서 SAR A/D 변환기의 복원된 신호는 그림 10과 같으며, 복원

그림 9. 제안하는 SAR A/D 변환기 레이아웃 Fig. 9. The layout of proposed SAR A/D converter

그림 10. 입력신호 복원파형 Fig. 10. The Restoration wavef

Fig. 10. The Restoration waveform of input signal

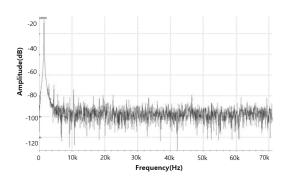

그림 11. FFT 모의실험 결과 Fig. 11. The FFT simulation result

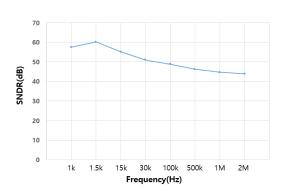

된 출력신호의 FFT 모의실험을 통한 스펙트럽 결과는 그림 11과 같다. 모의실험 결과, SNDR은 58.08dB, 유효비트수는 9.5비트로 확인되었다. 그림12, 13은 각각 입력주파수에 따른 SNDR, 유효비트수의 변화를 나타내고 모든 실험의 샘플링주파수는 10MS/s으로 진행하였다. 입력신호는 1kHz부터 2MHz로 가변하였고, SNDR, ENOB은 1.5kHz에서 최댓값을 보였으며 입력주파수가 증가할수록 점차 감소하였다. 제안하는

그림 12. 입력신호 주파수 대비 SNDR의 변화 Fig. 12. The variation of SNDR versus input frequency

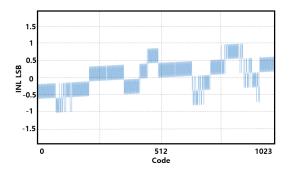

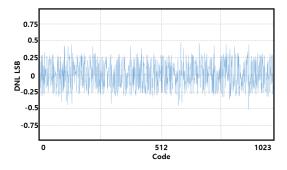

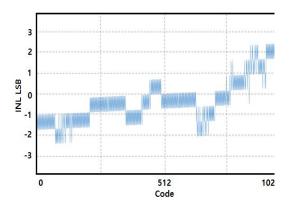

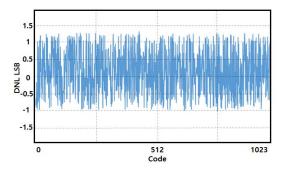

회로의 corner simultaion 조건을 TTT로 하였을 때 INL, DNL은 각각 ±1, 0.5 LSB로 측정되었다. 또한 corner simultaion 조건을 SSS로 하였을 때는 INL, DNL은 각각 ±2.5, 1.25 LSB로 측정 되었다.

제안하는 SAR A/D 변환기의 전력소모는 아날로 그, 디지털 각각 20,  $36\mu W$ 로 측정되었고, 저 전력 A/D 변환기 설계에 적용하다는 것을 확인하였다. 전체 성능평가지수(FoM)은 7.37fJ(step이다. 표 1에서는

그림 13. 제안하는 회로의 INL (TTT) Fig. 13. The INL of the proposed circuit (TTT)

그림 14. 제안하는 회로의 DNL (TTT) Fig. 14. The DNL of the proposed circuit(TTT)

그림 15. 제안하는 회로의 INL(SSS)

Fig. 15. The INL of the proposed circuit(SSS)

390nW

6.7

| Parameter         | [1]         | [2]          | [3]       | this work    |

|-------------------|-------------|--------------|-----------|--------------|

| Architecture      | 2bit/step   | 2bit/step    | 2bit/step | 2bit/step    |

| CMOS Process      | $0.18\mu m$ | $0.13 \mu m$ | 40nm      | $0.18 \mu m$ |

| Resolution(bit)   | 10          | 6            | 8         | 10           |

| Supply Voltage(V) | 0.6         | 1.2          | 0.8       | 1.8          |

| Speed             | 100kS/s     | 1.25GS/s     | 40.96MS/s | 10MS/s       |

| Input Range(Vpp)  | 1.2         | 1.2          | 1.2       | 1.2          |

| SNDR(dB)          | N/A         | N/A          | 45.8      | 58.02        |

| ENOB(bit)         | 9.2         | 5.8          | 7.32      | 9.5          |

| INL / DNL(LSB)    | 0.89 / 0.5  | N/A          | 1.5 / 1   | 1 / 0.5      |

32mW

N/A

표 1. 제안하는 SAR A/D converter 시뮬레이션 결과 Table 1. The proposed SAR ADC Simulation Result

Power

\* FoM(fJ/step)

그림 16. 제안하는 회로의 DNL(SSS) Fig. 16. The DNL of the proposed circuit(SSS)

제안하는 회로와 기존 회로의 성능을 비교하였다. 기존의 회로들은 스텝당 2비트 기법을 적용한 회로들로 구성하였다. 특히 본 논문은 기준전압 가변 비교기를 사용한 [2, 3]의 회로와 해상도를 비교하면, 분할방식을 통해 고해상도의 설계가 가능하고, 전체 성능평가지수(FoM)를 비교하면, 각각 7.37fJ/step과 16fJ/step으로서 본 논문에서 제안한 회로가 우수함을 알 수 있다.

# Ⅳ. 결 론

제안하는 SAR A/D 변환기는 기준전압 가변 비교기를 상위5비트에 이용하고, 스텝당 2비트 기법을 이용하여 변환속도를 향상시키고 전력 소모도 감소시켰다. 일반적인 스텝당 2비트 SAR A/D 변환기는 부가적인 회로에 의해 저 전력 설계에는 적합하지 못하다.

제안하는 회로는 상위5비트에 기준전압 가변 비교기를 이용하여 분할방식을 적용해 커패시터 D/A 변환기의 커패시터 개수를 일반적인 구조에서 4.3%만을 사용하여 전력 소모를 낮추었다.

$53 \mu W$

7.37

$107 \mu W$

$0.18 \mu m$  CMOS 공정을 이용하여 제작하였고, 10 MS/s의 변환속도에서 1.5 kHz의 정현파 입력에 대해 9.5비트의 ENOB이 측정되었다. INL, DNL은 각각  $\pm 1$ , 0.5 LSB이다. 제작된 SAR A/D 변환기의 면적은  $750 x700 \mu m^2$ 이며, 전력소모는  $56 \mu W$ 이다.

이때  $V_{ref}$ 는 1.2V이며, 외부전압으로 전력소모에 반영되지 않았다. 회로의 FoM은 7.37fJ/step으로 저전력 시스템에 적용될 수 있을 것으로 기대된다.

#### References

- [1] J. Jin, Y. Gao, and E. Sanchez-Sinencio, "An energy-efficient time-domain asynchronous 2 b/Step SAR ADC with a hybrid R-2R/C-3C DAC structure," *IEEE J. Solid-State Circuits*, vol. 49, no. 6, pp. 1383-1396, Jun. 2014.

- [2] Z. Cao, S. Yan, and Y. Li, "A 32 mW 1.25 GS/s 6b 2b/Step SAR ADC in 0.13 μ m CMOS," *IEEE J. Solid-State Circuits*, vol. 44, no. 3, pp. 862-873, Mar. 2009.

- [3] K. Yoshioka, A. Shikata, R. Sekimoto, T. Kuroda, and H. Ishikuro, "An 8 bit 0.3 0.8 V 0.2 40 MS/s 2-bit/Step SAR ADC with successively activated threshold configuring

<sup>\*</sup> FoM =  $Power/2^{ENOB} \cdot f_s$

- comparators in 40 nm CMOS," *IEEE Trans. VLSI*, vol. 23, no. 2, pp. 356-368, Feb. 2015.

- [4] H. K. Hong, W. Kim, and S. J. Park, "A 7b 1GS/s 7.2mW nonbinary 2b/cycle SAR ADC with register-to-DAC direct control," CICC, pp. 1-4, Sept. 2012.

- [5] D. Shi, S. Lee, and K. S. Yoon, "A 6-bit 500MS/s CMOS A/D converter with a digital input range detection circuit," *J. KICS*, vol. 38, no. 4, pp. 303-309, Jun. 2013.

- [6] K.-J. Kim, S. Park, and K. H. Ahn, "A study of CMOS power amplifier with the novel multi-loop transformer," *J. KICS*, vol. 2013, no. 11, pp. 17-18, 2013.

- [7] P. Nuzzo, C. Nani, C. Armiento, A. Sangiovanni-Vincentelli, J. Craninckx, and G. V. d. Plas, "A 6-Bit 50-MS/s threshold configuring SAR ADC in 90-nm digital CMOS," *IEEE Trans. CSI*, vol. 59, no. 1, pp. 88-92, Jan. 2012.

- [8] C. C. Liu, S. J. Chang, G. Y. Huang, and Y. Z. Lin, "A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure," *IEEE J. Solid-State Circuits*, vol. 45, no. 4, pp. 731-740, Apr. 2010.

- [9] G. Y. Lee, J. H. Kim, and K. S. Yoon, "Design of a low power 10bit flash SAR A/D converter," *J. KICS*, vol. 40, no. 4, pp. 613-618, Apr. 2015.

- [10] Y. Zhu, C. H. Chan, U. Chio, S. W. Sin, S. P. U, R. P. Martins, and F. Maloberti, "Split-SAR ADCs: Improved linearity with power and speed optimization," *IEEE Trans. VLSI*, vol. 22, no. 2, pp. 372-383, Feb. 2014.

#### 이 상 헌 (Sang-Heon Lee)

2015년 2월: 인하대학교 전자 공학과 학사 졸업

2017년 2월: 인하대학교 전자 공학과 석사 졸업

관심분야> 전자공학, 혼성신 호회로설계

#### 이 호용 (Ho-Yong Lee)

2017년 2월: 인하대학교 전자 공학과 학사 졸업 2019년 2월: 인하대학교 전자 공학과 석사 졸업 예정 <관심분야> 전자공학, 흔성신 호회로설계

#### 윤 광 섭 (Kwang-Sub Yoon)

1981년 : 인하대학교 전자공학 과 학사 졸업

1983년 : Georgia Institute Inc,Technology 전자공학과 석사 졸업

1989년 : Georgia Institute Inc, Technology 전자공학과 박 사 졸업

1984년 3월~1989년 2월: Georgia Institute of Technology Research Assistant.

1989년 3월~1992년 2월: Silicon Systems Inc, Tustin Calif. U.S.A Senior Design Engineer 1992년 3월~현재: 인하대학교 전자공학과 교수 <관심분야> 전자공학, 혼성신호 회로설계