# 고속용 p-MOS 트랜지스터에서 NBTI 스트레스에 의한 특성 인자의 열화 분석

종신회원 이 용 재\*, 이 종 형\*, 한 대 현\*

# The Degradation Analysis of Characteristic Parameters by NBTI stress in p-MOS Transistor for High Speed

Yongjae Lee\* Jonghyung Lee\* Daehyun Han\* Lifelong Members

요약

본 논문은 게이트 채널 길이 0.13 [四]의 p-MOS 트랜지스터에서 음 바이어스 온도 불안정(NBTI) 전류 스트레스 인가에 의한 게이트유기 드레인 누설(GIDL) 전류를 측정 분석하였다. NBTI 스트레스에 의한 문턱전압의 변화와 문턱전압아래 기울기와 드레인 전류 사이에 상관관계로부터, 소자의 특성 변화의 결과로 열화에 대한 중요한메카니즘이 계면 상태의 생성과 관련이 있다는 것을 분석하였다. GIDL 전류의 측정 결과로부터, NBTI 스트레스에 기인한 계면상태에서 전자-정공 쌍의 생성이 GIDL 전류의 증가의 결과를 도출하였다.

이런 결과로 부터, 초박막 게이트 산화막 소자에서 NBTI 스트레스 후에 증가된 GIDL 전류를 고려해야만 한다. 또한, 동시에 신뢰성 특성과 직류 소자 성능의 고려가 나노 크기의 CMOS 통신회로 설계의 스트레스 파라미터들에서 반드시 있어야 한다.

Key Words: GIDL, NBTI, p-MOS, Degradation, Subthreshold

#### **ABSTRACT**

This work has been measured and analyzed the device degradation of NBTI (Negative Bias Temperature Instability) stress induced the increase of gate-induced-drain-leakage(GIDL) current for p-MOS transistors of gate channel length 0.13 [µm]. From the relation between the variation of threshold voltage and subthreshold slop by NBTI stress, it has been found that the dominant mechanism for device degradation is the interface state generation. From the GIDL measurement results, we confined that the EHP generation in interface state due to NBTI stress led to the increase of GIDL current.

As a results, one should take care of the increased GIDL current after NBTI stress in the ultra-thin gate oxide device. Also, the simultaneous consideration of reliability characteristics and dc device performance is highly necessary in the stress parameters of nanoscale CMOS communication circuit design.

# I. 서 론

초고속/집적용 실리콘 전계효과 트랜지스터에서 게이트 길이가 나노 스케일로 축소되면서 통신회로 설계 시에 소자의 채널길이와 게이트 산화막의 두께의 축소에 따른 p, n-MOS 트랜지스터 소자에서 신뢰성 향상을 위한 연구가 진행 중 이다. 신뢰성에크게 관련된 게이트유기 드레인 누설 전류, 문턱전

논문번호: KICS2009-08-369, 접수일자: 2009년 8월 21일, 최종논문접수일자: 2009년 12월 10일

<sup>※</sup> 이 논문은 동의대학교 교내연구(2008AA167)의 결과로 연구되었습니다.

<sup>\*</sup> 동의대학교 전자공학과(yjlee@deu.ac.kr)

압, 문턱전압아래 기울기와 드레인 전류 등 특성 파 라미터들의 열화가 음 바이어스 스트레스 하에서 심 각한 영향이 나타나고 있다.<sup>[1,2]</sup> 또 소자가 고온에서 동작할 때 게이트의 음전압에 의하여 소자의 특성이 불안정 상태가 될 수 있는 소위 회로 응용 시에 음 바이어스 온도 불안정(NBTI) 상태가 발생될 수 있 는데, 이 NBTI 현상으로 인한 개별 소자의 문턱전 압이 증가하여 드레인 전류가 감소하는 현상이 일어 나서 소자의 수명시간 단축에 영향을 주게 된다. 이 런 음 바이어스 온도 불안정 현상은 n-MOS 트랜지 스터 보다는 p-MOS 트랜지스터 소자에서 더 많이 일어난다고 보고[3,4]되고 있다. 이러한 얇은 게이트 산화막은 소자가 차단 상태인 게이트에 영 볼트의 전압을 인가하고 드레인 전압을 인가할 때 드레인 영역의 공핍층에서 전자가 가전대로부터 전도대로 터널링이 일어나는 게이트유기 드레인 누설(GIDL) 전류가 흐르게 된다. 이런 현상의 원인으로 많은 연 구자들이 두 가지 원인으로 설명하며, 그 중 하나는 실리콘-산화막에서 계면 트랩(Nit)의 생성에 의한 것 이고, 다른 하나는 계면에서 발생된 수소가 게이트 산화막으로 확산해 가면서 양전하(Nox)를 발생 시킨 다는 설명이다.<sup>[5]</sup> 이러한 소자에서의 부작용이 고속 고집적의 통신소자 응용에서 신뢰성 문제로 부각되 고 있다.[6]

본 연구는 따라서 음 바이어스 온도 불안정 (NBTI) 현상에 의한 소자 열화 메카니즘, 소자 수명 시간, 열화 모델링, 그리고 스트레스 유기 누설 전류에 관한 연구로써 초박막 게이트 최신 공정 소자의 p-MOS 트랜지스터에서 음 바이어스 온도 불안정 전류가 게이트유기 드레인 누설(GIDL) 전류에 미치는 영향과 문턱전압 변화, 문턱아래 전류 기울기와 드레인 전류의 특성 변화와 그의 형성 메커니즘과 결과를 분석하고자 한다.

# Ⅱ. 소자 제작

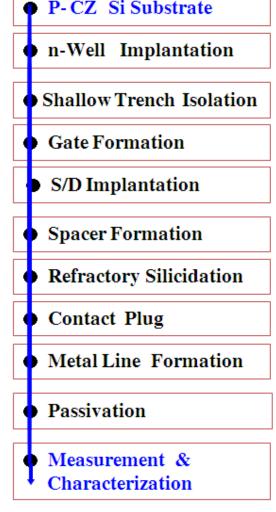

소자 간의 격리는 얕은 트랜치 격리(STI) 구조의 공정

그림. 1. 소자 단면과 제작을 위한 주요 공정 흐름도 Fig. 1. Device section and major process flow for fabrication

이며, 게이트의 다결정과 소스/드레인의 접촉 저항과 직력 저항 성분을 줄이기 위해 티타늄을 스퍼터 시켜 티타늄 실리사이드 형성시켰다.

소자의 드레인의 직렬저항은  $6 \times 10^{14}$  [ $\Omega$ cm²], 면저항은 200 [ $\Omega$ /sq]의 최신 공정으로 제작하였으며, 소자의 정상 동작 공급전원 1.5 [V], 개별 트랜지스터 지연시간은 2.5 [ps]의 최신 소자로 제작되었다.

# Ⅲ. 측정 및 결과 고찰

#### 3.1 NBTI 와 GIDL 전류와의 관계

스트레스 인가 방법에서 음 바이어스 온도 불안정 (NBTI) 전류 스트레스를 인가 하기위한 실험 조건은 드

레인은 접지시키고, 게이트-소스에는 소스에 양의 전압, 게이트에 음의 전압을 인가시킨다. 스트레스 온도는 105 [°C] 이며 게이트의 스트레스 전압은 -5 [V]에서 0.5 [V] 씩 증가시켜 -8 [V]까지 변화시켰으며, 스트레스 시간을 변화시키며 소자의 특성을 측정하였다.

게이트유기 드레인 누설(GIDL) 전류를 측정할 태 드 레인 전압  $V_D$  =-5 [V], 게이트 전압  $V_g$  =0 [V]로 정의하였으며, 소스 부분은 부유시켰으며, 기판은 전위의 변화를 줄이기 위하여 접지를 시켰다.

음 바이어스 온도 불안정 현상(NBTI)이 MOS 트랜지스터의 게이트가 장 채널 소자는 NBTI 현상을 제거할수 있지만, 단 채널에서는 이 현상에 의한 영향이 중요한특성으로 나타난다. 단 채널 소자에서 NBTI 현상의 문제를 세 가지 방법으로 완화 시킬 수 있다. 첫째로 소자의 구조에서 게이트 면적을 넓게 하는 것이고, 둘째는 차세대 모델이 레이아웃에서 게이트 모양이 좌우 대칭으로 설계하여 NBTI 열화를 예측하여 완화 시킬 수 있으며, 마지막으로 새로운 특성화 방법이 개발<sup>41</sup>되어서 이런 종류의 동요를 제거할 수 있다.

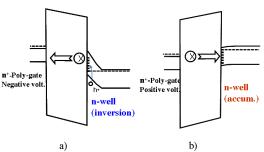

그림 2에서 GIDL발생 원인을 설명하는 모델로 a)는 음 바이어스 온도 불안정 전류 스트레스 동안 게이트 전 극으로 수소 확산과 계면에서 Si-H 결합 파괴가 되면서 계면트랩이 생성되는 과정이며, b)는 양 바이어스 동안 실리콘에서 현수 본드가 보호되고, 수소 원자가 계면으로 되돌아가는 과정인 계면 트랩 패시베이션 과정이다. 여기에서 X는 수소 원자를 의미한다. (4.6) 이 그림을 통하여 스트레스 시간에 따라서 드레인 전류의 양이 변화하는 특성을 확인할 수 있다. 그 이유로는 여러 보고 5.6)에서 잘 알려진 것과 같이 계면 트랩의 발생과 양 전하의 생성과 증가의 원인을 들 수 있다. 이때 음 바이어스 온도 불안정 현상에 의한 계면 트랩밀도(Nit) 생성 및 양전하 생성을 다음과 같은 반응식으로 설명할 수 있다.

a) b) 그림 2. 에너지 밴드 상태 a) 계면 트랩 생성 : b) 계면 트랩 페시베이션

Fig. 2. Energy band states a) Interface trap  $N_{it}$  generation b) Interface trap  $N_{it}$  passivation

$$Si_{3} - Si - H \rightarrow Si_{3} - Si^{0} + X_{interface}$$

$$X_{interface} \rightarrow X_{bulk}^{+}$$

(1)

여기에서,  $Si_3$ -Si는 계면 트랩 생성밀도( $N_{ii}$ )를 나타내고, X는 수소 원자를 나타낸다. 실리콘/산화막 경계면에서 수소 원자가 나와서  $N_{ii}$ 를 생성하고 이 수소 원자가산화막 내에 양전하를 생성시킨다. 그러나  $N^{\dagger}$ 다결정 실리콘을 게이트로 사용할 경우는 측정 전압 인가 시에 게이트로 주입되는 전자에 의하여 이 양전하가 현격히 감소하게 되어 계면 트랩에 의하여 GIDL 등 소자의특성이 열화 되는 것으로 분석되고 있다.

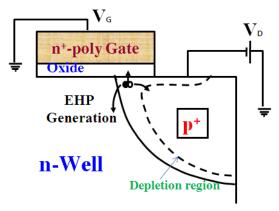

소자에서 게이트 유기드레인 누설(GIDL) 전류의 메 카니즘을 설명하기 위한 것이 그림 3으로, GIDL 전류의 생성 원인은 다른 많은 연구에서 보고[3],[4],[8]된 것과 같 이 게이트와 드레인 사이에 높은 전압을 인가하였을 때 드레인 영역에 깊은 공핍영역이 형성되어서 공핍층의 전계가 크게 된다. 이로 인해 공핍층에서 전자정공쌍이 생성되는데 정공은 드레인으로 주입이 되고 전자는 기 판이나 게이트로 주입이 된다. 여기에 대한 구체적인 설 명이 그림 4이며, 전계가 크면 드레인의 가전대의 전자 가 전도대로 터널링(Band to Band Tunneling)이 일어나 게 되며, 실리콘/산화막 경계면에 계면 트랩(N<sub>it</sub>)이 있으 면 트랩 어시스트 터널링이 더 많이 일어나는 원인이 되 어서 GIDL 전류가 증가하게 되고 이는 곧 큰 누설전류 성분이 된다. 이때 GIDL 전류밀도(J)는 게이트 산화막 의 전계(E<sub>s</sub>)의 함수로서 식(1)로 나타낼 수 있으며, 게이 트 산화막의 전계와 드레인 사이에 인가된 전압에 의한 전계와 GIDL 전류와의 관계는 다음식과 같다.[2]-[4]

그림 3. MOS 구조에서 게이트 유기 드레인 누설 전류의 형 성 메카니즘

Fig. 3 Generation mechanism of GIDL current in MOS structure

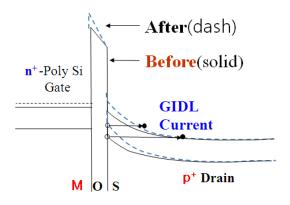

그림 4. MOS에서 GIDL 전류 생성 전후의 에너지 밴드 형태 Fig. 4. Energy band shape of GIDL current generation before and after in MOS

$$J_d = A \cdot E_s \cdot \exp(-\frac{B}{E_s}) A = \frac{2qm_r E_g^2 \pi}{h^3}$$

$$B = \frac{\pi \sqrt{m_r} E^{\frac{3}{2}}}{qh \sqrt{2}}$$

(2)

$$E_s = \frac{(V_{DG} + V_{fb} - 1.2)}{3T_{ar}} \tag{3}$$

$$V_{fb} = -\phi_{ms} - \frac{Q}{C_{ax}} \tag{4}$$

위 식(2)는 드레인 전류의 형성의 주요 인자를 나타내며, 식(3)의 의미는 드레인 전류가 전계( $\mathbf{E}_s$ )에 일차적으로 영향을 미치고, 드레인 전류에 자연지수적으로 반비례하며, 식(4)의 전계의 크기 중 평탄대 전압( $\mathbf{V}_{fb}$ )은 계면 트랩에 의해 많은 영향을 받는다. 그림 4는 이런 게이트유기 드레인 누설 전류의 형성을 구체적으로 에너지 밴드로 설명한 것이다.

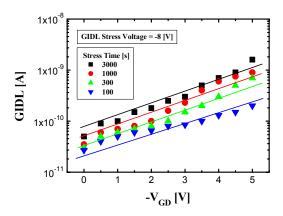

결과로 부터 스트레스 시간의 증가에 따라 게이트 유기 드레인 누설 전류가 증가하는 것으로 나타났는데, 이런 GIDL 전류 증가는 NBTI 스트레스에 의한 계면 트랩의 생성이 증가하여 이로 인한 전자의 증가에 의한 전류의 증가로 설명할 수 있다. 이런 현상을 바탕으로 그림 5는 NBTI 스트레스 후 게이트-드레인 전압( $V_{GD}$ )에 따른 GIDL 전류 측정 결과로서 스트레스 인가 전압을 -8 [V]고정시키고,  $V_{GD}$ 를 0 [V]에서 GIDL 전류를 측정하고 0.5[V] 씩 증가 시키면서 -5 [V]까지 증가시키면서 각전압에서 GIDL 전류의 최대값을 테이터로 하고, 또 스트레스 시간 변화에 따른 GIDL 전류의 특성 변화를 나

그림 5. 드레인-게이트 전압에 따른 GIDL 전류의 특성 Fig. 5. Characteristics of GIDL current according to draingate voltage

타낸 각각의 결과를 종합적으로 나타낸 것이다.

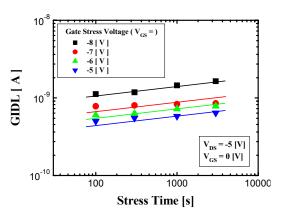

그림 6은 시간에 따른 게이트 유기 드레인 누설 GIDL 전류의 변화를 측정/추출한 결과이다. 게이트 스트레스 전압 $V_g$ 을 -5 [V]에서 -8 [V]까지 변화시키면서 GIDL의 전류 변화를 측정하였다. 소자에 인가하는 스트레스 시간과 게이트 스트레스 전압의 증가에 따라서 GIDL 전류가 파워법칙<sup>[5]</sup>( $I_{DS} \propto t^n$ )에 거의 접근하는 결과로 나타났다.

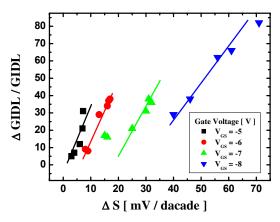

그림 7은 문턱전압 아래 기울기 차이( $\Delta$ S)에 대한 게이트유기 드레인 누설 차이( $\Delta$ GIDL)와의 상관도를 나타낸 결과이다. 전체적으로는  $\Delta$ S와  $\Delta$ GIDL이 비례관계에 있지만, 게이트 스트레스 전압이 -5 [V]와 -8 [V]에서 각각 큰 차이가 나타났다. 스트레스 시간이 길 때는  $\Delta$ S와  $\Delta$ GIDL이 일대일 비례관계가 성립이 아니며, 앞에서 NBTI 스트레스에 의해서 계면 트랩이 생성되고

그림 6. 스트레스 시간 변화에 따른 GIDL 전류의 특성 Fig. 6. Characteristics of GIDL current according to stress time variations

그림 7. 게이트 전압 변화에 따른 문턱전압 아래 기울기와 GIDL 차이와의 상관관계

Fig. 7. Relationship between  $\Delta S$  and  $\Delta GIDL$  according to stress time

이로 인해 소자의 열화 특성에서 주된 원인으로 분석되었는데, NBTI 스트레스 인가 후 GIDL 전류 또한 계면 트랩의 생성에 의해서 증가하는 특성을 나타낸다.

# 3.2 게이트 전압과 NBTI 전류 스트레스 시간 의 존성

NBTI 현상을 줄이는 방법으로 최근에 개발된 게이트 전류( $I_g$ ) 방법 $^{[1],[2]}$ 으로 소자의 열화 특성을 분석하고자한다. 이 방법은 실리콘/산화막 계면에서 포획 전화와 산화막 벌크에서 물리적 현상을 기초로 한 산화막 전계를 개량하여 나타난 게이트 직접 터널링 전류 $J_{DT}$ 에서 변화결과를 이용한다. 게이트 전류의 이동 특성을 관측하여전 유효 포획 밀도( $\triangle N_{t,eff}$ )를 전계( $\triangle E$ )에서 변화로부터 추출할 수 있다. 이때, 다음 식을 사용함으로써 문턱전압 차이( $\triangle V_{th}$ )가 전 유효 포획 밀도와 산화막 커패시턴스와 관계하며 이는 게이트 직접 터널링 전류와 전계계수인자와의 관계로 차이가 나는 것으로 나타났다.

$$\Delta V_{th} = \frac{q\Delta N_{,eff}}{C_{ox}} = -\frac{1}{C_{ox}} \frac{\epsilon_{ox} \overrightarrow{E_o}}{H_{DT}} ln(\frac{J_{DT}}{J_{DTo}})$$

(4)

$$H_{DT} = \frac{d \ln \left[ J_{DT}(\overline{E}_{ox}) \right]}{d \left( \Delta \overline{E} / \overline{E_o} \right)} \Big|_{\frac{\Delta E}{\overline{E_o}} = 0} \tag{5}$$

여기에서,  $C_{ox}$ 는 게이트 산화막의 단위 커패시턴스이고,  $J_{DTo}$ 는 게이트 직접 터널링 전류이고,  $E_{o}$ 는 처음 산화막 전계이고,  $H_{DT}$ 는  $J_{DT}[In(J_{DT}/J_{DTo}) = H_{DT} \triangle E/E_{o}]$ 의 전계 계수이다.

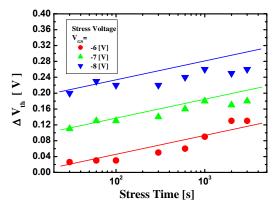

그림 8은 문턱전압의 차이의 수식적인 관계를 소자와 연계하여 동일한 스트레스 조건에서 게이트전류 방법을 이용한 NBTI 특성 결과로 스트레스 시간에 따른 문턱전 압차이( $\Delta V_{th}$ )를 나타낸 결과이다. 스트레스 인가 후 문 턱 전압은 시간의 증가에 따라 증가 하였으며, 게이트의 스트레스 전압이 클수록  $\Delta V_{th}$ 의 변화가 큰 것을 확인 할 수 있다.  $\Delta V_{th}$ 는 앞에서 설명한 것과 같이  $N_{tr}$ 의 생성 으로 설명할 수 있다. 문턱전압의 변화는 산화층 내의 전 하 생성으로 설명할 수 있는데 NBTI에 의하여 2 종류의 전하가 생성될 수 있지만, n<sup>+</sup>-다결정 실리콘을 게이트로 사용할 경우는 N<sub>it</sub>의 생성으로 설명할 수 있음을 문턱전 압 아래 기울기(subthreshold slope) 변화로부터 확인 할 수 있다. 또한 그림 8로 부터 문턱전압 변화량  $\Delta V_{th} \propto T_s^n$ 의 관계가 있는 것을 확인 할 수 있다. 게이 트 전압( $V_g$ )= -7[V] 일 때는 지수값  $n \simeq 0.3$  정도로 추 출 되었으며, 스트레스 전압이 증가할수록 n은 거의 일 정한 결과를 보이는데, 이는 타 연구<sup>[3], [4], [6]</sup>의 결과와도 거의 일치하는 결과로 나타났다.

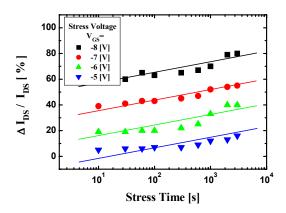

드레인 전류가 각각의 스트레스 시간에 대한 드레인 전류 변화율( $\Delta I_{ds}$ )로 측정한 전체 결과가 그림 9이다. 스트레스 시간의 증가에 따라서  $\mathbf{x}$ 축의 로그축과  $\mathbf{y}$ 축의 측정값에서 거의 선형적으로 일정한 증가 추세를 나타나는 이런 특성도 파워법칙( $\mathbf{I}_{ds} \propto \mathbf{t}^{\mathbf{n}}$ )[5]에 거의 접근하는 결과와 거의 일치하는 분석이다.

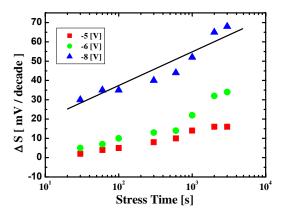

그림 10은 게이트 전압의 스트레스 조건과 동일한 상태에서 시간에 따른 문턱전압 아래 기울기 차이 ( $\Delta$ S)를 나타낸 결과의 그림으로, NBTI 스트레스 후에는 S가 증가 하였는데 그 이유는 식(6)에서 계면트랩 밀도 $N_{ii}$ 에 의

그림 8. 게이트 전류 방법을 이용한 스트레스 시간에 따른 문턱전압 차이 변화(  $\Delta$ VTH)

Fig. 8. Threshold voltage difference variation ( $\Delta$ VTH) using Ig method

그림 9. 스트레스 시간에 따른 드레인 전류 변화율 Fig. 9. Drain current variations according to stress time

그림 10. 스트레스 시간에 따른 문턱전압이래 기울기차이( $\Delta S$ ) Fig. 10. Subthreshold slope( $\Delta S$ ) variations according to stress time

한 커패시턴스Cir의 영향으로 분석할 수 있다. [5], [6]

$$S = 60m V (1 + \frac{C_{dep} + C_{it}}{C_{ox}})$$

(6)

여기에서,  $C_{ox}$ 는 산화층 커패시턴스이고,  $C_{dep}$ 는 공핍 층 커패시턴스이다.

즉, 그림 8, 그림 9와 그림 10의 분석을 통하여 NBTI 현상의 주된 영향은 계면트랩에 의한 영향으로 확인 할수 있다. 즉 산화층에서의 양전하 생성은 문턱전압의 변화를 가져오지만 S의 변화는 크지 않게 된다. 그러나 계면상태 생성(N<sub>it</sub>)생성은 문턱아래 기울기(S) 변화뿐만아니라 문턱전압도 변화시키게 된다.

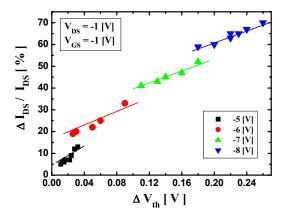

그림 11은 드레인 전류 변화량과 문턱전압 차이( $\Delta$   $V_{th}$ )의 상관관계를 나타낸 결과로 NBTI 현상으로 인하여 문턱전압이 변하고, 이로 인한 소자의 특성 열화로 인

그림 11. 스트레스 시 간에 따른 드레인 전류 변화율과 문턱 전압 차이와의 상관관계

Fig.11. Relationship between  $\Delta \mathrm{Id}$  and  $\Delta \mathrm{Vth}$  according to stress time

하여 드레인 전류의 감소를 나타낸다. 포화 영역에서 드레인 전류는 문턱전압 변화에 선형적으로 비례관계로 나타났는데, 이는 타연구<sup>[1], [6]</sup>의 결과와도 일치하는 것이다.

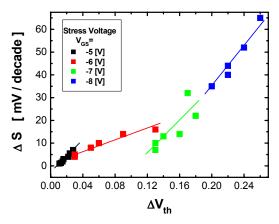

문턱전압 차이( $\Delta V_{th}$ )와 문턱아래전압 기울기 차이 ( $\Delta S$ )의 상관관계를 나타낸 결과가 그림 12이며, 문턱전 압의 변화량이 증가하는 동안  $\Delta S$  값도 증가하는 것으로 나타났다.

$\Delta V_{th}$ 와  $\Delta S$ 가 선형적으로 비례하는 것은 앞에서 설명하였던 것과 같이 NBTI 스트레스에 의하여 2종류의전하가 생성되지만. 게이트 전국 N $^{+}$ 다결정 실리콘을 게이트로 사용할 경우는 계면 트랩의 생성으로 소자에서게이트 산화막으로 인한 열화가 주된 메카니즘으로 분석되다. $^{[1],[5],[7]}$

그림 12. 스트레스 시 간에 따른 문턱전압 차이와 문턱전압 아래 기울기와의 상관관계 Fig. 12. Relationship between  $\Delta S$  and  $\Delta V$ th according

to stress time

# Ⅳ. 결 론

고속용 통신소자 혹은 회로에서 제품의 신뢰성을 위해서 기존에 거의 고려하지 않았던 특성인자인 NBTI 스트레스의 고려가 요구된다. 이는 NBTI 스트레스로 인하여 문턱전압과 드레인 전류 및 문턱전압 아래 기울기의 특성 열화 이외에 누설전류가 증가하는 것을 확인할 수 있었다. 문턱전압 아래 기울기 차이( $\Delta$ S)와 게이트 유기드레인 누설 전류 차이( $\Delta$ GIDL)가 일차적인 선형 비례관계가 아닌 것으로부터 GIDL 전류의 증가가 계면트랩 생성 외에 또 다른 인자의 원인도 있을 것으로 분석이 된다.

스트레스 전류의 인가 전과 후의 스트레스 시간 변화에 따른 문턱전압의 변화량과 문턱전압 아래 기울기(S)의 변화량, 드레인 전류 변화, 게이트 유기 드레인 누설전류 등의 파라미터 특성 분석을 통하여 음 바이어스 온도 불안정(NBTI) 전류 스트레스로 생성된 2 종류의 전하 중에서 계면 트랩 생성(N<sub>it</sub>)이 MOSFET 소자에서 열화 특성의 주된 메카니즘임을 확인하였다. 특히 스트레스 인가 후의 소자에서 GIDL 전류 증가는 계면트랩 생성으로 인한 전류 성분으로 판단이 된다.

추후 지속적으로, 신뢰성으로 고려한 초고속/고집적을 위한 MOS 트랜지스터의 응용을 위해서 소자에서 음바이어스 온도 불안정(NBTI) 전류의 스트레스에 기인하는 최신 공정과 소자 개발에 따른 특성 파라미터의 계속적인 측정과 분석을 통하여 소자의 신뢰성과 성능을 향상시키고자한다.

#### 참 고 문 헌

- [1] H. Hwang, et al "Contribution of Interface States and Oxide Traps to the Negative Bias Temperature Instability of High-k pMOSFETs" IEEE EDL, Vol.30, No.3, pp.291-293, Mar. 2009.

- [2] S. J. Lin et al "Gate-Induced Drain Leakage (GIDL) Improvement for Millisecond Flash Anneal (MFLA) in DRAM Application" IEEE Trans. Electron Devices, Vol.56, No. 8, pp.1608-1617, Aug. 2009.

- [3] M. Gurfinkel, S. Yoram, et al "Enhanced Gate Induced Drain Leakage current in HfO2 MOSFETs due to remote interface trapassisted tunneling," in IEDM Tech. Dig., 2006, pp.14-16, Dec. 2006.

- [4] Ali Khakifirooz "MOSFET Performance

- Scaling -Part II: Future Directions" IEEE Trans. Electron Devices, Vol.55, No.6, pp.1401-1408, June. 2008.

- [5] I.S. Han et al "New Observation of Mobility and Reliability Dependance on Mechanical Film Stress in Strained Silicon CMOSFETs" IEEE Trans. on ED, Vol.55 No.6 pp.1352-1358. June. 2008.

- [6] Y. Yang et al. "Characteristics and Fluctuation of Negative Bias Temperature Instability in Si Nanowire FET" IEEE EDL, Vol.29, No.3, pp.242-245, March. 2008.

# 이 용 재 (Yong-jae Lee) 종신회원

1981년 2월 경북대학교 전자공 학과

1983년 2월 연세대학교 전자공 학과 공학석사

1986년 8월 연세대학교 전자공 학과 공학박사

1988년 3월~현재 동의대학교 전자공학과 교수

<관심분야> 고속 소자, 반도체공정, 아날로그 IC 설계

# 한 대 현 (Dae-Hyun Han) 종신회원

1986년 8월 경북대학교 전자공 학과

1990년 2월 포항공대 전기전자 공학 공학석사

1996년 8월 포항공대 전기전자 공학과 공학박사

1999년 3월~현재 동의대학교 전자공학과 교수

<관심분야> RF 소자 및 회로

#### 이 종 형 (Jong-Hyung Lee) 종신회원

1987년 2월 연세대학교 전자공학과

1990년 2월 연세대학교 전자공학과 공학석사

2000년 5월 EE, Virginia Tech 공학박사

2002년 3월~현재 동의대학교 전자공학과 교수

<관심분야> 광통신 및 저전력 CMOS 회로